WM8940

16

Rev 4.4

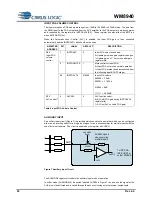

AUDIO INTERFACE TIMING

–

SLAVE MODE

BCLK

FRAME

t

BCH

t

BCL

t

BCY

DACDAT

ADCDAT

t

LRSU

t

DS

t

LRH

t

DH

t

DD

Figure 3 Digital Audio Data Timing

– Slave Mode

Test Conditions

DCVDD=1.8V, DBVDD=AVDD=SPKVDD=3.3V, DGND=AGND=SPKGND=0V, T

A

=+25

o

C, Slave Mode, fs=48kHz, MCLK= 256fs,

24-bit data, unless otherwise stated.

PARAMETER

SYMBOL

MIN

TYP

MAX

UNIT

Audio Data Input Timing Information

BCLK cycle time

t

BCY

81.38

ns

BCLK pulse width high

t

BCH

32.55

ns

BCLK pulse width low

t

BCL

32.55

ns

FRAME set-up time to BCLK rising edge

t

LRSU

10

ns

FRAME hold time from BCLK rising edge

t

LRH

10

ns

DACDAT hold time from BCLK rising edge

t

DH

10

ns

DACDAT set-up time to BCLK rising edge

t

DS

10

ns

ADCDAT propagation delay from BCLK falling edge

t

DD

15

ns

Note:

BCLK period should always be greater than or equal to MCLK period.