DS726PP2

13

CS4525

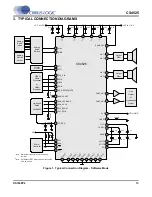

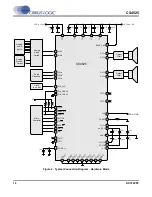

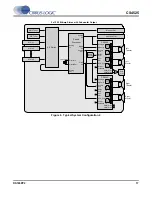

3. TYPICAL CONNECTION DIAGRAMS

+8 V to +18 V

31

30

25

V

P

36

VP

VP

VP

12

V

D

470 µF

0.1 µF

0.1 µF

0.1 µF

0.1 µF

470 µF

35

RAMP_CAP

0.1 µF

10 µF

+3.3 or +5 V

Analog

Audio

Inputs

43

AUX_SDOUT

Analog

Audio

Switch

AINR

20

AINL

19

10

23

22

28

33

34

37

38

27

P

G

ND

P

G

ND

P

G

ND

P

G

ND

P

G

N

D

P

G

ND

P

G

ND

P

G

ND

D

G

ND

*Note: Resistors are required for I²C control port

operation.

OUT1

OUT2

Output

Filter

35

32

OUT3

OUT4

Output

Filter

29

26

PWM_SIG2

39

40

PWM_SIG1

Line

Output

- or -

Headphone

Output

Analog

Monitor

Output

Crystal

24.576 MHz

XTI

XTO

48

47

MPEG

Audio

Processor

- or -

HDMI

Receiver

SDIN

6

LRCK

4

SCLK

5

46

SYS_CLK

7

HP_DETECT/MUTE

Lip-Synch

Delay

NJU26902

+2.5V

VD_REG

11

0.1 µF

10 µF

AUX_SCLK

44

DLY_SDOUT

41

DLY_SDIN

42

AUX_LRCK/AD0

45

Micro-

Controller

RST

8

INT

1

SDA

3

SCL

2

2 k

Ω

22

k

Ω

2 k

Ω

VD

*

*

AGND

14

VA_REG

13

AFILTA

17

AFILTB

18

FILT+

15

VQ

16

0.1 µF

10 µF

150 pF

150 pF

10 µF

1 µF

LVD

9

VD or GND

OCREF

21

16.2 k

Ω

Note: On release of RST, AD0 is read as input on the

AUX_LRCK line.

22

k

Ω

†

†

22 k

Ω

Figure 1. Typical Connection Diagram - Software Mode

CS4525