4-10

SAM9N12/CN11-EK User Guide

11186A–ATARM–29-Nov-12

A 3-state buffer is in serial with NAND flash’s CE signal, with PB1 to give a manually disable manner for

NAND boot.

4.3.8

UART DBGU

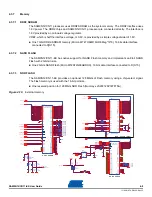

The Universal Asynchronous Receiver Transmitter features a two-pin UART that can be used for com-

munication and trace purposes and offers an ideal medium for in-situ programming solutions.

This two-pin UART (TXD and RXD only) is buffered through an RS232 transceiver MN16 and brought to

the DB9 male connector J11.

Figure 4-11. UART

4.3.9

JTAG Interface

The SAM9N12/CN11-EK board includes a JTAG interface port (J4), to provide debug level access to the

processor. The JTAG port is a 20-pin male connector. This port provides the required interface for in-cir-

cuit emulators such as ARM’s Multi-ICE.

Figure 4-12. JTAG

VD DI OP0

R136

100K

R 135

100K

C 91

100nF

C 94

100nF

MN 16

MAX3232CSE

T1IN

11

T2IN

10

R1O UT

12

R2O UT

9

T1OU T

14

T2OU T

7

R 1I N

13

R 2I N

8

V+

2

C1+

1

C1-

3

C2+

4

C2-

5

V-

6

VCC

16

GND

15

C92

100nF

C 93

100nF

C90

100nF

J 11

5

4

3

2

1

9

8

7

6

10

11

PA10

(D TXD)

UART

PA9

(D RXD)

VDD I OP0