AT32WB415

Series Reference Manual

2022.04.13

Page 47

Ver 2.00

4

Clock and reset manage (CRM)

4.1 Clock

AT32WB415 series provide different clock sources: HEXT oscillator clock, HICK oscillator clock, PLL

clock, LEXT oscillator and LICK oscillator.

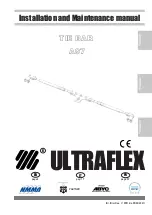

Figure 4-1 AT32WB415 clock tree

USB

Divider

/1,1.5,

2,2.5,

3,3.5,

4

USB48M

To USB interface

/128

LEXT

RTCCLK

To RTC

LICK RC

40 kHz

RTCSEL[1:0]

LICK

To WDT

WDTCLK

Clock Output

CLKOUT

ADC

Divider

/2,4,6,8,12,16

To ADC1 ADCCLK

Max.28 MHz

Peripheral

clock enable

To AHB peripheral/memory

HICK RC

48 MHz

/6

HICK48M

HICKDIV

HEXT_IN

HEXT OSC

4-25 MHz

HEXT

HEXT

PLLRCS

PLLCLK

PLLCLK

LEXT OSC

32.768 kHz

LEXT_IN

LEXT_OUT

LEXT

LICK

HICK_TO_SCLK

SCLKSEL

CFD

HICK8M

HEXT

HICK

SCLK

Max. 150 MHz

12S1/2 CLK

Peripheral

clock enable

AHB

Divider

/1,2...512

HCLK

Max.150MHz

CPU FCLK

/8

CPU SysTick

CLKOUT

Divider

/1,2..512

Peripheral

Clock enable

PCLK1/2

Max.75 MHz

To APB1/2 peripheral

Max.150 MHz

to TMRxCLK

Peripheral

clock enable

x1,x 2

APB1/2

Divider

/1,2,4,8,16

/2

HEXT

Divider

/2

*2,*3,*4

*16,

,*64,

PLL

PLLMULT

PLLHEXTDIV

HICK4M

PCLK2

Max.75 MHz

/2

/4

PLLCLK

PLLCLK

HICK

HEXT

SCLK

USB48M

ADCCLK

LICK

LEXT

CLKOUT_SEL

AHB, APB1 and APB2 all support multiple frequency division. The AHB domain has a maximum of 150

MHz, and both APB1 and APB2 are up to 75 MHz.

4.1.1

Clock sources

High speed external oscillator (HEXT)

An external clock source can be provided by HEXT bypass. Its frequency can be up to 25 MHz. The

external clock signal should be connected to the HEXT_IN pin.

High speed internal clock (HICK)

The HICK oscillator is clocked by a high-speed RC in the microcontroller. The internal frequency of the

HICK clock is 48 MHz. Although it is less accurate, the HICK clock frequency of each device is calibrated

to 1% accuracy (25°C) in factory. The factory calibration value is loaded in the HICKCAL[7: 0] bit of the

clock control register. The RC oscillator speed may be affected by voltage or temperature variations.

Thus the HICK frequency can be trimmed using the HICKTRIM[5: 0] bit in the clock control register.

The HICK clock signal is not released until it becomes stable.

PLL clock

The HICK or HEXT clock can be used as an input clock source of the PLL, and these clocks must be a

range of 2 M and 16 MHz. The input clocks and multiplication factor must be selected before enabling

PLL. The reason is that the configuration parameters cannot be changed once PLL is enabled. The PLL

clock signal is not released before it becomes stable.

Low speed external oscillator (LEXT)

The LEXT oscillator provides two clock sources: LEXT crystal/ceramic resonator and LEXT bypass.

LEXT crystal/ceramic resonator: