AT32F435/437

Series Reference Manual

2022.11.11

Page 309

Rev 2.03

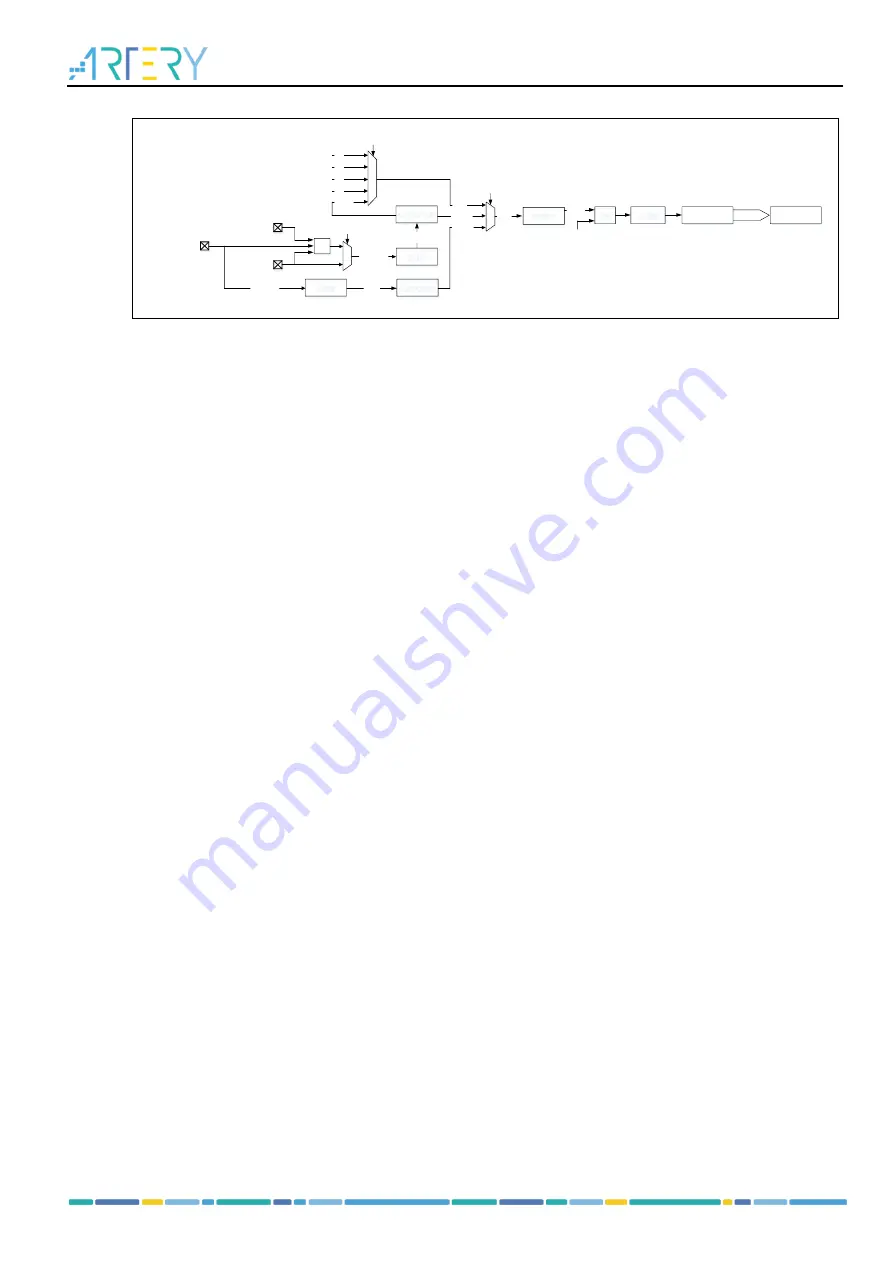

Figure 14-506

Channel 1 input stage

Capture

CNT counter

C1DT

C1P/C1CP

edge detector

C1IN

C1IFP1

C2IFP1

STCI

C1C

C1IDIV

input divider

C1IPS

C1IF

XOR

TMRx_CH2

TMRx_CH3

TMRx_CH1

C1INSEL

C1IRAW

filter

C1DF

C1SWTR

C1EN

C2IF

C2IRAW

C2P/C2CP

edge detector

filter

C2DF

IS2

IS1

IS0

C1INC

IS3

STIS

OR

Input mode

In input mode, the TMRx_CxDT registers latch the current counter values after the selected trigger signal

is detected, and the capture compare interrupt flag bit (CxIF) is set to 1. An interrupt/DMA request will

be generated if the CxIEN or CxDEN bit are enabled. If the selected trigger signal is detected when the

CxIF is set, a capture overflow event occurs. The TMRx_CxDT register overwrites the recorded value

with the current counter value, and the CxRF is set to 1.

To capture the rising edge of C1IN input, following the configuration procedure mentioned below:

Set C1C=01 in the TMRx_CxDT register to select the C1IN as channel 1 input

Set the filter bandwidth of C1IN signal (CxDF[3: 0])

Set the active edge on the C1IN channel by writing C1P=0 (rising edge) in the TMRx_CCTR

register

Program the capture frequency division of C1IN signal (C1DIV[1: 0])

Enable channel 1 input capture (C1EN=1)

If needed, enable the relevant interrupt or DMA request by setting the C1IEN bit in the

TMRx_IDEN register or the C1DEN bit in the TMRx_IDEN register

Timer Input XOR function

The timer input pins (TMRx_CH1, TMRx_CH2 and TMRx_CH3) are connected to the channel 1

(selected by setting the C1INSE in the TMRx_CTRL2 register) through an XOR gate.

The XOR gate can be used to connect Hall sensors. For example, connect the three XOR inputs to the

three Hall sensors respectively so as to calculate the position and speed of the rotation by analyzing

three Hall sensor signals.

PWM input

The PWM input mode applies to channel 1 and channel 2. To enable this mode, map the C1IN and C2IN

to the same TMRx_CHx, and configure the CxIFPx of channel 1/2 to trigger slave timer controller reset.

The PWM input mode can be used to measure the period and duty cycle of input signal. The period and

duty cycle of channel 1 can be measured as follows:

Set C

1C=2‘b01 to set C1IN as C1IFP1;

Set C

1P=1’b0 to set C1IFP1 rising edge active;

Set C

2C=2‘b10 to set C2IN as C1IFP2;

Set C

2P=1’b1 to set C1IFP2 falling edge active;

S

et STIS=3’b101 to set C1IFP1 as the slave timer trigger signal;

Set S

MSEL=3‘b110 to set the slave timer in reset mode;

Set C

1EN=1’b1 and C2EN=1’b1 to enable channel 1 and input capture.

In these configurations, the rising edge of channel 1 input signal triggers capture and saves captured

values to the C1DT register, and channel 1 input signal rising edge resets the counter. The falling edge

of channel 1 input signal triggers capture and saves captured values to the C2DT register. The period

and duty of channel 1 input signal can be calculated through C1DT and C2DT respectively.