AT32F425

Series Reference Manual

2022.03.30

Page 230

Ver 2.01

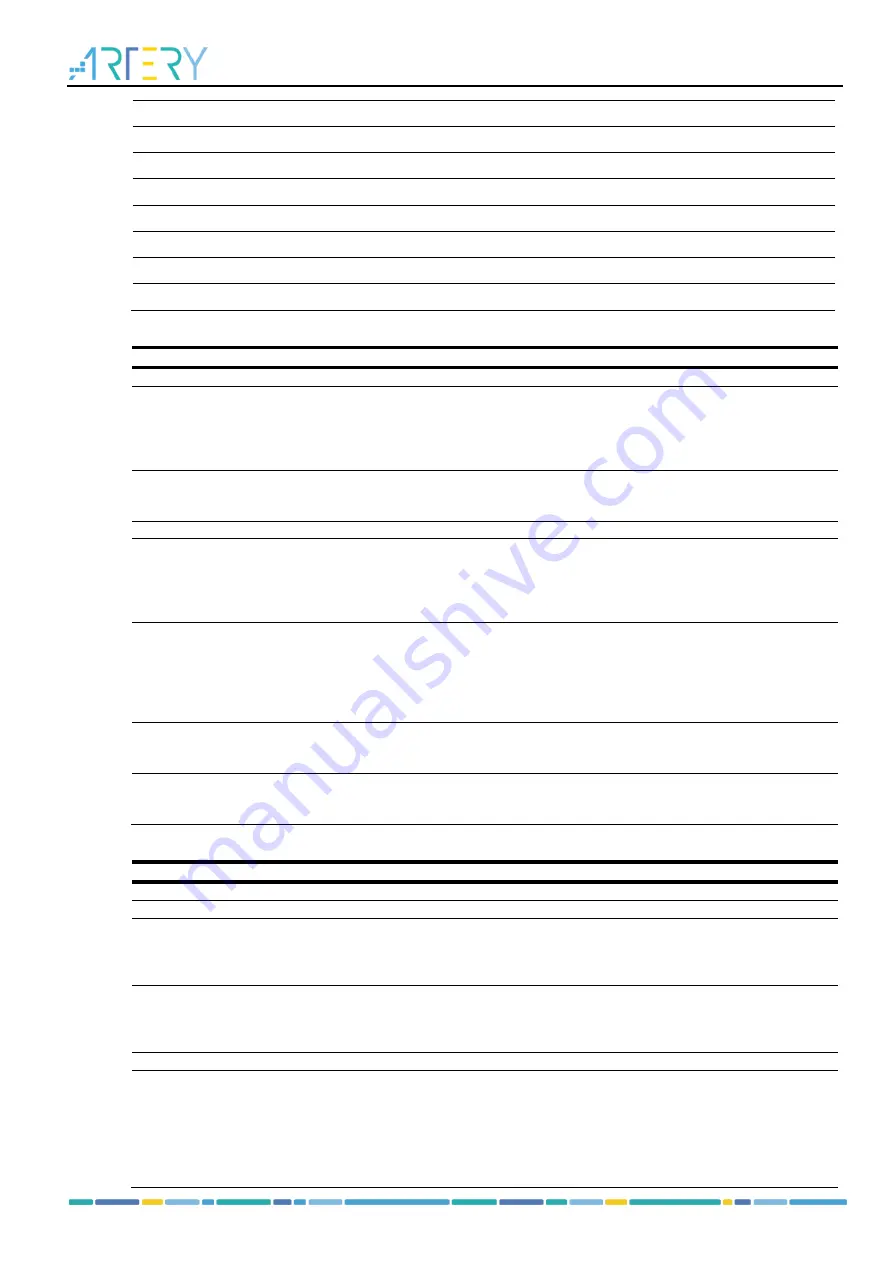

TMR15_DIV

0x28

0x0000

TMR15_PR

0x2C

0x0000

TMR15_RPR

0x30

0x0000

TMR15_C1DT

0x34

0x0000

TMR15_C2DT

0x38

0x0000

TMR15_BRK

0x44

0x0000

TMR15_DMACTRL

0x48

0x0000

TMR15_DMADT

0x4C

0x0000

14.4.4.1 TMR15 control register1 (TMR15_CTRL1)

Bit

Register

Reset value

Type

Description

Bit 15: 10

Reserved

0x00

resd

Kept at its default value

Bit 9: 8

CLKDIV

0x0

rw

Clock divider

00: Normal

01: Divided by 2

10: Divided by 4

11: Reserved

Bit 7

PRBEN

0x0

rw

Period buffer enable

0: Period buffer is disabled

1: Period buffer is enabled

Bit 6: 4

Reserved

0x0

resd

Default value

Bit 3

OCMEN

0x0

rw

One cycle mode enable

This bit is use to select whether to stop counting at an

update event

0: The counter does not stop at an update event

1: The counter stops at an update event

Bit 2

OVFS

0x0

rw

Overflow event source

This bit is used to select overflow event or DMA request

sources.

0: Counter overflow, setting the OVFSWTR bit or overflow

event generated by slave timer controller

1: Only counter overflow generates an overflow event

Bit 1

OVFEN

0x0

rw

Overflow event enable

0: Enabled

1: Disabled

Bit 0

TMREN

0x0

rw

TMR enable

0: Enabled

1: Disabled

14.4.4.2 TMR15 control register2 (TMR15_CTRL2)

Bit

Register

Reset value

Type

Description

Bit 31: 11 Reserved

0x0

resd

Kept at its default value.

Bit 10

C2IOS

0x0

rw

Channel 2 idle output state

Bit 9

C1CIOS

0x0

rw

Channel 1 complementary idle output state

OEN = 0 after dead-time:

0: C1OUTL=0

1: C1OUTL=1

Bit 8

C1IOS

0x0

rw

Channel 1 idle output state

OEN = 0 after dead-time:

0: C1OUT=0

1: C1OUT=1

Bit 7

Reserved

0x0

resd

Kept at its default value.

Bit 6: 4

PTOS

0x0

rw

Master TMR output selection

This field is used to select the TMRx signal sent to the

slave timer.

000: Reset

001: Enable

010: Update

011: Compare pulse