CYC1000 User Guide

www.arrow.com

Page | 38

January 2020

5.2.7.7

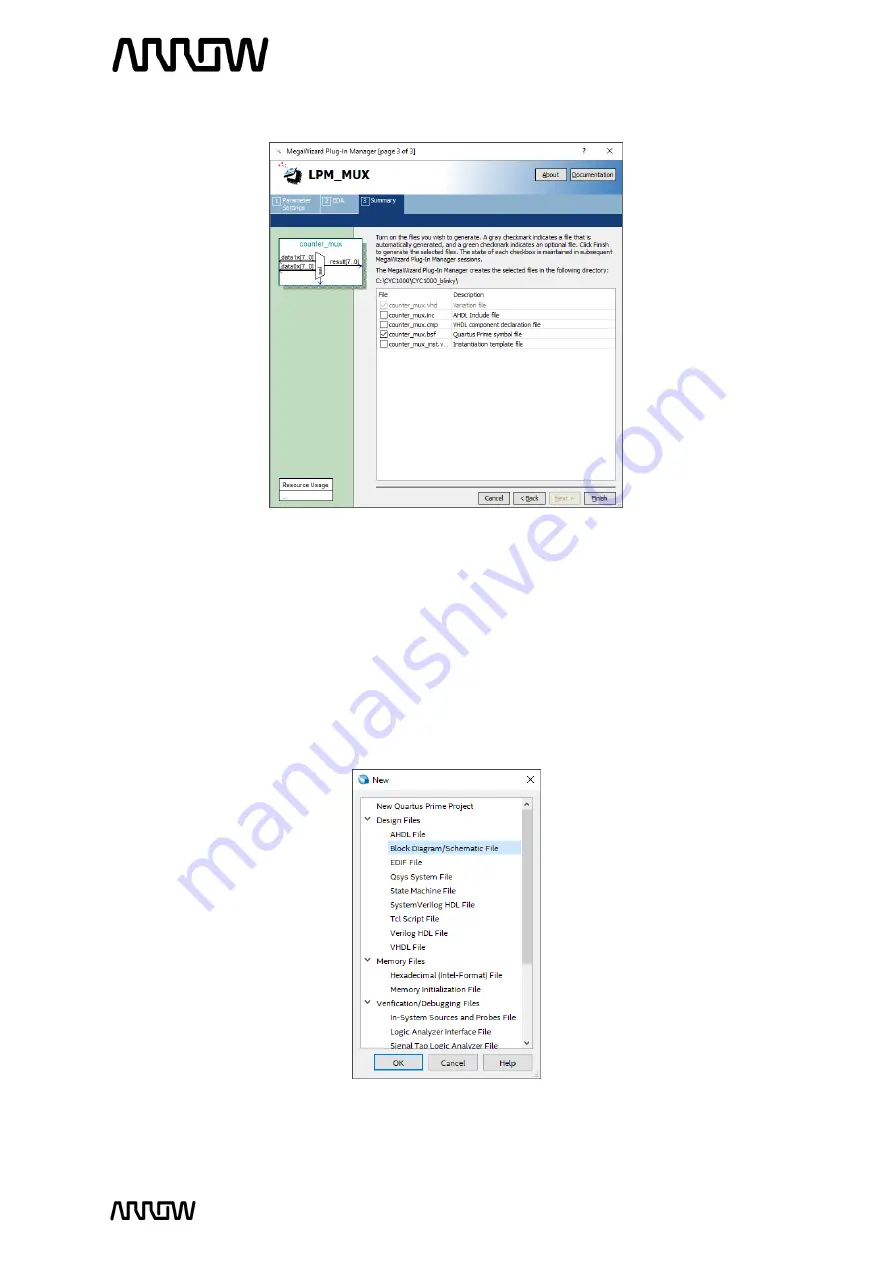

Select counter_mux.bsf checkbox to generate a symbol for our schematic design.

5.2.7.8

Click

“

Finish

”.

5.2.8

Adding the Components to the Schematic

The next step would be to connect all three components together.

5.2.8.1

To do so, select File menu, then select New and select Block Diagram/Schematic File.

5.2.8.2

Click

“

OK

”.

A new schematic will be created, where the components can be added.