CYC1000 User Guide

www.arrow.com

Page | 36

January 2020

5.2.6.9

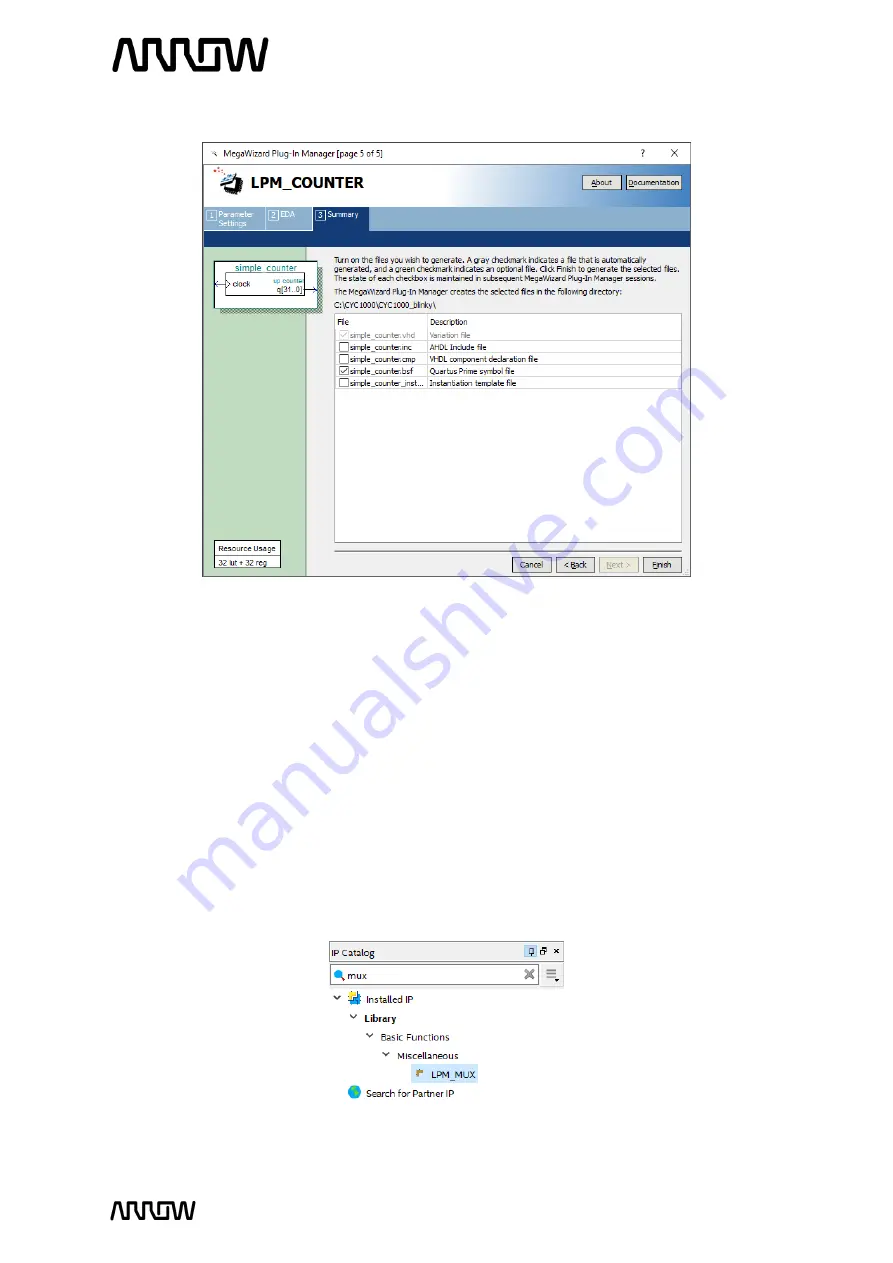

Select simple_counter.bsf checkbox to generate a symbol for our schematic design.

5.2.6.10

Click

“

Finish

”.

The counter is now created.

5.2.7

Create and Configure the Multiplexer

The next step is to create a mux component. This mux will be used along with a push button on

the CYC1000 board to control the speed of the counter, where the counter outputs will be seen

on the LEDs.

5.2.7.1

To create this mux, select IP Catalog and expand

Basic Functions

→

Miscellaneous

and

select LPM_MUX or type mux in the search field.

5.2.7.2

Click

“

Add

”.