A10.2

Accessing the feature identification registers

Software can identify the Advanced SIMD and floating-point features using the feature identification

registers in the AArch64 Execution state only.

The Cortex-A76 core only supports AArch32 in EL0, therefore none of the feature identification

registers are accessible in the AArch32 Execution state.

You can access the feature identification registers in the AArch64 Execution state using the

MRS

instruction, for example:

MRS <Xt>, ID_AA64PFR0_EL1 ; Read ID_AA64PFR0_EL1 into Xt

MRS <Xt>, MVFR0_EL1 ; Read MVFR0_EL1 into Xt

MRS <Xt>, MVFR1_EL1 ; Read MVFR1_EL1 into Xt

MRS <Xt>, MVFR2_EL1 ; Read MVFR2_EL1 into Xt

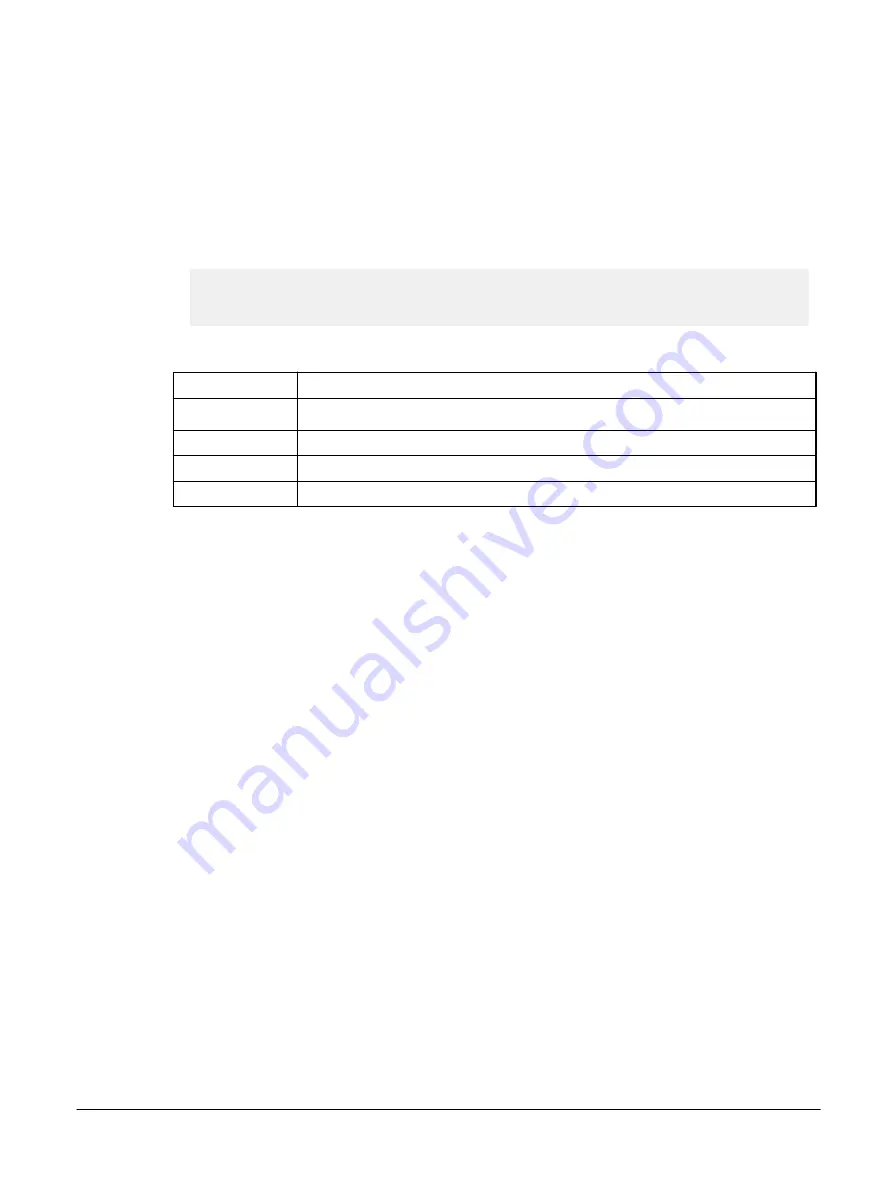

Table A10-1 AArch64 Advanced SIMD and scalar floating-point feature identification registers

Register name

Description

ID_AA64PFR0_EL1 See

B2.61 ID_AA64PFR0_EL1, AArch64 Processor Feature Register 0, EL1

.

MVFR0_EL1

See

B5.4 MVFR0_EL1, Media and VFP Feature Register 0, EL1

.

MVFR1_EL1

See

B5.5 MVFR1_EL1, Media and VFP Feature Register 1, EL1

.

MVFR2_EL1

See

B5.6 MVFR2_EL1, Media and VFP Feature Register 2, EL1

.

A10 Advanced SIMD and floating-point support

A10.2 Accessing the feature identification registers

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

A10-117

Non-Confidential

Содержание Cortex-A76 Core

Страница 4: ......

Страница 22: ......

Страница 23: ...Part A Functional description ...

Страница 24: ......

Страница 119: ...Part B Register descriptions ...

Страница 120: ......

Страница 363: ...Part C Debug descriptions ...

Страница 364: ......

Страница 401: ...Part D Debug registers ...

Страница 402: ......

Страница 589: ...Part E Appendices ...

Страница 590: ......