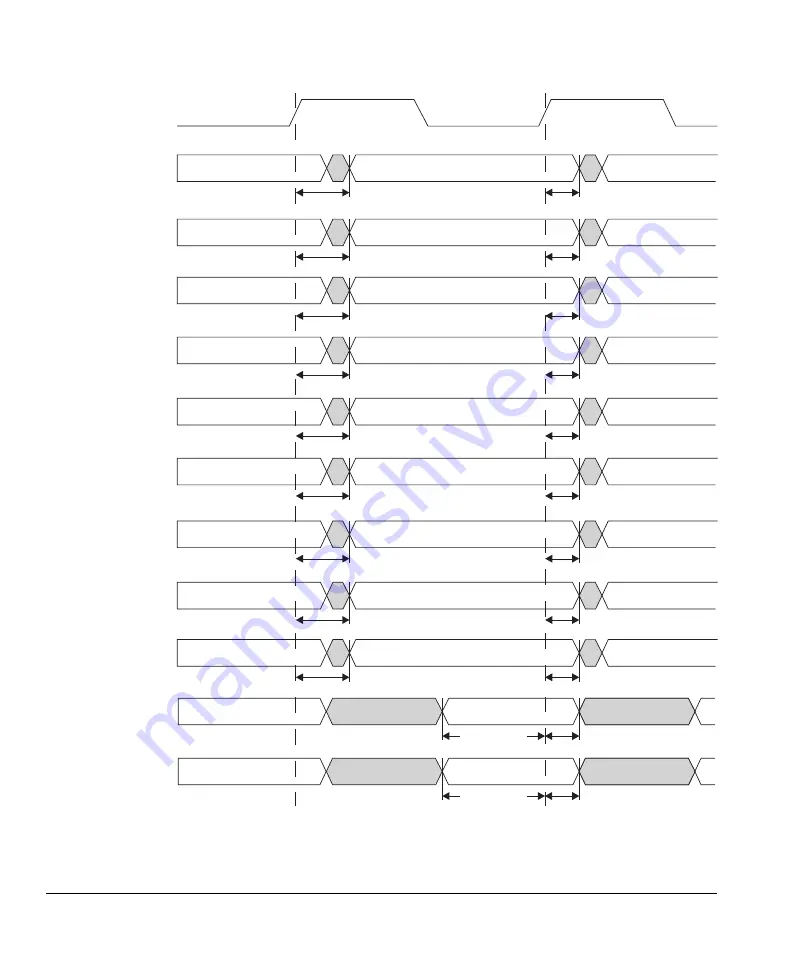

AC Parameters

B-10

Copyright © 2000 ARM Limited. All rights reserved.

ARM DDI 0186A

Figure B-10 ETM interface timing

CLK

ETMIA[31:1]

ETM31TO25[31:25]

ETM15TO11[15:11]

ETMInMREQ

ETMISEQ

ETMITBIT

ETMINSTREXEC

ETMINSTRVALID

ETMDA[31:0]

ETMRDATA[31:0]

ETMWDATA[31:0]

ETMMAS[31:0]

ETMnWAIT

ETMDMORE

ETMDnMREQ

ETMDnRW

ETMDABORT

ETMCHSD[1:0]

ETMPASS

ATMPLATECANCEL

ETMDBGACK

ATMRNGOUT[1:0]

ETMEN

FIFOFULL

ETMBIGEND

ETMHIVECS

ETMPROCID

ATMPRODCDWR

T

ovtminst

T

ohetminst

T

ovetmdata

T

ohetmdata

T

ovetmstat

T

ohetmstat

T

ovtmicti

T

ohetmiuctl

T

ovetmnwait

T

ohetmnwait

T

ovetmdctl

T

ohetmdctl

T

ovetmcfg

T

ohetmcfg

T

ovetmcpif

T

ohetmcpif

T

ovetmdbg

T

ohetmdbg

T

ihetmfifull

T

ihetmen

T

isetmen

T

isetmfifofull

Содержание ARM966E-S

Страница 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...