Coprocessor Interface

Copyright © ARM Limited 2000. All rights reserved.

7-11

7.5

CDP

CDP

instructions normally execute in a single cycle. Like all the previous cycles,

nCPMREQ is driven LOW to signal when an instruction is entering the Decode and

then the Execute stage of the pipeline. If the instruction really is to be executed, the

CPPASS signal is driven HIGH during the Execute cycle. If the coprocessor can

execute the instruction immediately it drives CHSDE[1:0] with LAST. If the

instruction requires a busy-wait cycle, the coprocessor drives CHSDE[1:0] with WAIT

and then CHSEX[1:0] with LAST.

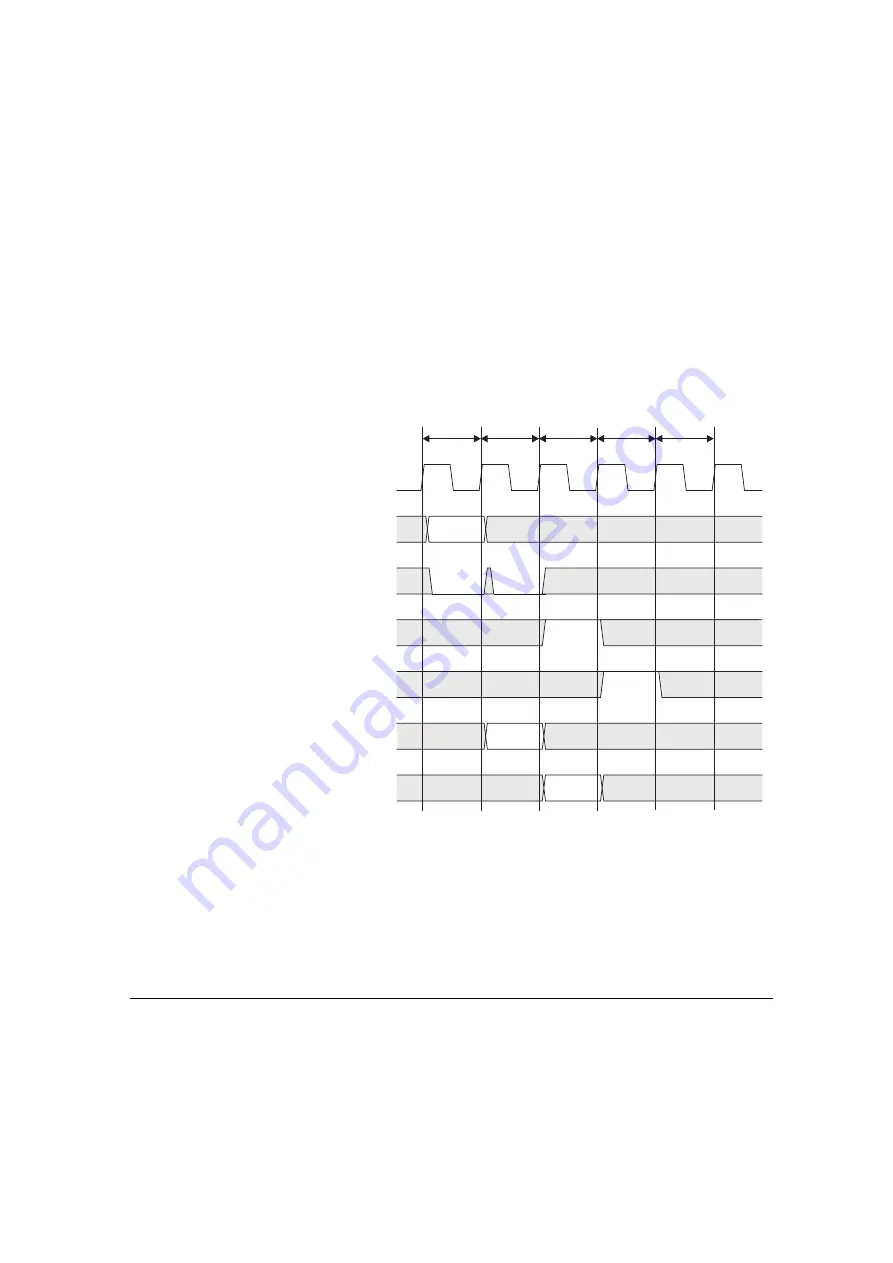

Figure 7-5 shows a

CDP

cancelled because the previous instruction caused a Data Abort.

Figure 7-5 Late cancelled CDP

The

CDP

instruction enters the Execute stage of the pipeline and is signaled to execute

by CPASS. In the following cycle CPLATECANCEL is asserted. This causes the

coprocessor to terminate execution of the

CDP

instruction and for it to cause no state

changes to the coprocessor.

Ignored

LAST

CLK

nCPMREQ

CPINSTR[31:0]

CHSDE[1:0]

CHSEX[1:0]

CPPASS

CPLATECANCEL

CPRT

Decode

Execute

Memory

(Latecancelled)

Coprocessor

pipeline

Fetch

Instruction

aborted

Содержание ARM946E-S

Страница 1: ...ARM DDI 0155A ARM946E S Technical Reference Manual ...

Страница 6: ...vi Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A 04 Limited Confidential ...

Страница 54: ...Programmer s Model 2 34 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 70: ...Caches 3 16 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 78: ...Protection Unit 4 8 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 98: ...Bus Interface Unit and Write Buffer 6 14 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 112: ...Coprocessor Interface 7 14 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...