UG-1134

EVAL-ADAU1467Z

Rev. A (Draft) | Page 30 of 55

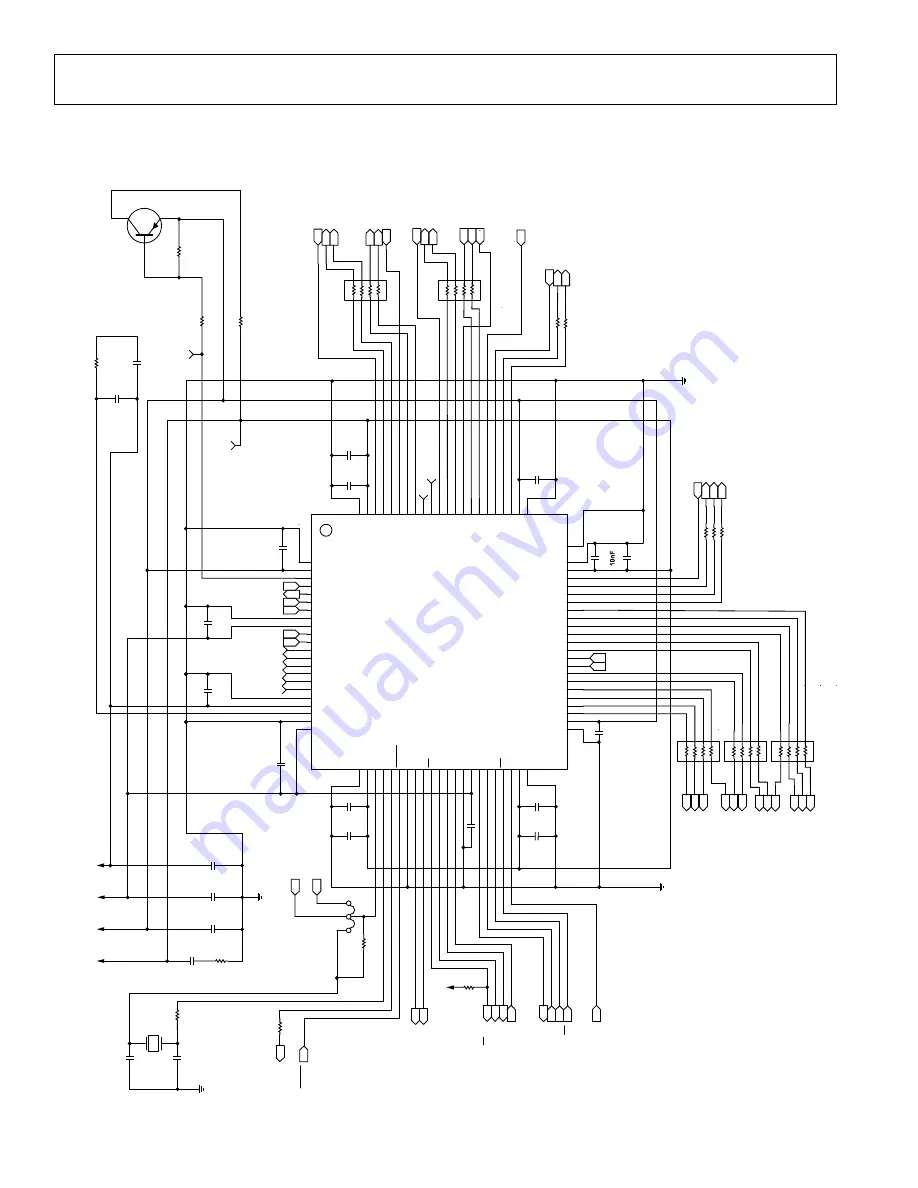

EVALUATION BOARD SCHEMATICS AND ARTWORK

Figure 83.

Audio Processor Schematic

EXPOSED

PAD

DVDD

DV

DD

DV

DD

IOVD

D

IOV

D

D

GND

G

ND

IOV

D

D

AV

DD

DV

DD

G

ND

PVD

D

To Sla

ve

Cont

rol

Port (U

SBi)

To

Mast

er

Cont

rol P

ort

Seco

nd

ary I2C

To

CODE

C &

Pe

riphe

ra

l Cnt

l Out

T

o

J19 &

S

DP

Co

n

n

ect

o

r

To J

9

To J

9

To C

OD

E

C

From SDP

Connector

(& Header J8)

From ADCs

(CODEC)

T

o

DACs

(CO

DE

C)

T

o

M

ic Can

vas

C

onne

c

tor

To

Switch S8

From Mic

Canvas

Connector

From

Header J8

X

TA

L OS

C

C14

0.

10u

F

C9

0.

10u

F

C12

0.

10u

F

C17

0.

10u

F

C43

0.

10u

F

C41

0.

10u

F

C45

0.

10u

F

C40

0.

10u

F

C22

0.

10u

F

C20

0.

10u

F

C46

10u

F

C13

10u

F

C99

10u

F

C18

10u

F

C15

10n

F

C16

10n

F

C42

C44

10n

F

C10

22p

F

C8

22p

F

Y1

12.

288 M

Hz

R9

100R

R10

33R2

PVDD

PLLFILT

DGND

IOVD

D

DG

ND

DV

DD

X

TA

LIN

/M

C

LK

X

TA

LOU

T

CL

KO

UT

R

ESET

DG

ND

S

CL

2_M

/M

P

24

S

DA2_M

/M

P

25

SS_

M/

MP0

MO

SI

_

M/

MP1

SC

L

K

_

M/

MP2

MI

SO

_

M/

MP3

DG

ND

VDRI

VE

SP

DIFIN

SP

DIFOU

T

MP14

MP15

AGND

AVDD

AUXADC0

AUXADC1

AUXADC2

AUXADC3

AUXADC4

AUXADC5

AUXADC6

AUXADC7

PG

ND

DG

ND

DV

DD

S

E

LFB

OOT

S

S

/ADDR0

M

O

S

I/

ADDR1

S

CL

K/

S

CL

MI

SO

/SD

A

23

24

25

26

27

28

29

30

31

32

33

34

35

36

44

43

42

41

40

39

38

37

IOV

D

D

IOVD

D

19

20

21

22

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

2

1

DGND

72

71

70

69

68

67

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

S

DAT

AI

O

0/

M

P

16

S

DAT

AI

O

1/

M

P

17

S

DAT

AI

O

2/

M

P

18

S

DAT

AI

O

3/

M

P

19

IOV

D

D

DG

ND

BCL

K_I

N0

L

RCL

K_I

N0/

M

P

10

S

DAT

A_I

N0

BCL

K_I

N1

L

RCL

K_I

N1/

M

P

11

S

DAT

A_I

N1

T

HD_M

T

HD_P

BCL

K_I

N2

L

RCL

K_I

N2/

M

P

12

S

DAT

A_I

N2

BCL

K_I

N3

L

RCL

K_I

N3/

M

P

13

S

DAT

A_I

N3

DV

DD

DG

ND

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

89

DGND

DVDD

SDAT

AIO

4/M

P20

SDAT

AIO

5/M

P21

SDAT

AIO

6/M

P22

SDAT

AIO

7/M

P23

SDAT

A_OUT

3

BCLK_O

UT3

LRCL

K_OUT

3/M

P9

SDAT

A_OUT

2

BCLK_O

UT2

LRCL

K_OUT

2/M

P8

MP7

MP6

SDAT

A_OUT

1

BCLK_O

UT1

LRCL

K_OUT

1/M

P5

SDAT

A_OUT

0

BCLK_O

UT0

LRCL

K_OUT

0/M

P4

IOVD

D

DGND

EP

U2

ADAU1467W

BCP

Z

300

C11

0.

10u

F

R19

33R2

R18

33R2

R23

33R2

R22

33R2

33R2

33R2

33R2

R20

0R47

AUXADC7

AUXADC6

AUXADC5

AUXADC4

AUXADC3

AUXADC2

T

HD_M

T

HD_P

R148

33R2

R75

R150

R151

R12

R14

R35

0R00

B

A

J3

DV

DD

IOV

D

D

3V

3_A

3V

3_A

R

ESET

S

CL

K

MO

SI

SS

SP

DIFOU

T

SP

DIFIN

SS_

M

MO

SI

_

M

S

CL

K_M

MI

SO

_

M

MI

SO

S

E

LFB

OOT

WRI

TE

BACK_MP

6

MP7

CL

KO

UT

AUXADC0

AUXADC1

MP14

MP15

MP2

4

MP2

5

L

RCL

K_O

UT

2

BCL

K_O

UT

2

BCL

K_O

UT

3

S

DAT

A_O

UT

2

L

RCL

K_O

UT

3

S

DAT

A_O

UT

3

S

DAT

A_I

N3

BCL

K_I

N3

L

RCL

K_I

N2

BCL

K_I

N2

S

DAT

A_I

N1

L

RCL

K_I

N1

BCL

K_I

N1

S

DAT

A_I

N0

L

RCL

K_I

N0

BCL

K_I

N0

DAC3_S

DAT

AI

O

7

DAC2_S

DAT

AI

O

6

DAC1_S

DAT

AI

O

5

ADC1_S

DAT

AI

O

4

M

C_L

E

D_S

DAT

A_S

DAT

AI

O

3_M

P

19

S

DAT

AI

O

0

M

C_L

E

D_S

CL

K_S

DAT

AI

O

2_M

P

18

M

C_T

DM

8_S

DAT

AI

O

1_M

P

17

S

DAT

A_O

UT

1

L

RCL

K_O

UT

1

S

DAT

A_O

UT

0

BCL

K_O

UT

0

L

RCL

K_O

UT

0

L

RCL

K_I

N3

S

DAT

A_I

N2

S

DP

_M

CL

K_I

N

E

X

T

E

RNAL

M

CL

K I

NP

UT

BCL

K_O

UT

1

PVD

D

P

LLFILT

R11

4K32

C21

150p

F

C19

5.

6n

F

R107

1k00

R105

0R00

R106

0R00

B

C

E

Q1

S

T

D2805

V

DRI

V

E

DV

DD

R73

10k0

IOV

D

D

33R2

33R2

DRAFT

Содержание SigmaDSP ADAU1463

Страница 44: ...UG 1134 EVAL ADAU1467Z Rev A Draft Page 44 of 55 Figure 110 EVAL ADAU1467ZLayout Top Copper D R A F T...

Страница 45: ...EVAL ADAU1467Z UG 1134 Rev A Draft Page 45 of 55 Figure 111 EVAL ADAU1467Z Layout Layer 2 Ground D R A F T...

Страница 47: ...EVAL ADAU1467Z UG 1134 Rev A Draft Page 47 of 55 Figure 113 EVAL ADAU1467Z Layout Layer 4 Power D R A F T...

Страница 48: ...UG 1134 EVAL ADAU1467Z Rev A Draft Page 48 of 55 Figure 114 EVAL ADAU1467Z Layout Layer 5 Ground D R A F T...

Страница 49: ...EVAL ADAU1467Z UG 1134 Rev A Draft Page 49 of 55 Figure 115 EVAL ADAU1467Z Layout Bottom Copper D R A F T...