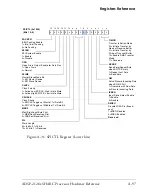

I/O Processor Registers

A-110

ADSP-2126x SHARC Processor Hardware Reference

Table A-33. Parallel Port Register (PPCTL) Bit Definitions

Bit

Name

Definition

Default

0

PPEN

Parallel Port Enable.

Enables if set, (= 1) or disables if

cleared, (= 0) the parallel port. Clearing this bit clears

FIFO and status. If an

RD

,

WR

, or ALE cycle has already

started, it completes normally before the port is disabled.

The parallel port is ready to transmit or receive 2 cycles

after enabling. An ALE cycle always occurs before the first

read or write cycle after PPEN is enabled.

0

5–1

PPDUR

Parallel Port Duration.

The duration of Parallel Port data

cycles is based on core-clock and controlled by these five

bits as follows:

00000 = Reserved

00001 = Reserved

00010 = 2 Wait States = 3 Core Clock Cycles;

66 MHz throughput

00011 = 3 Wait States = 4 Core Clock Cycles;

50 MHz throughput

00100 = 4 Wait States = 5 Core Clock Cycles;

40 MHz throughput

00101 = 5 Wait States = 6 Core Clock Cycles;

33 MHz throughput

...

11111 = 31 wait states; 6.25MHz throughput

Bit 1 = 1

Bit 2=1

Bit 3=1

Bit 4=0

Bit 5=1

6

PPBHC

Bus Hold Cycle.

Inserts a bus hold cycle at the end of

every access (read or write cycle) if set, (= 1) or no bus

hold cycle occurs if cleared, (= 0). During a BHC address

and/or data continue to be driven for one cycle.

1

7

PP16

Parallel Port External Data Width.

Selects the external

data width to 16 bits if set, (= 1) or 8 bits if cleared, (= 0).

0

8

PPDEN

Parallel Port DMA Enable.

Enables if set, (= 1) DMA on

the parallel port or disables DMA if cleared, (= 0). When

PPDEN is cleared, any DMA requests already in the pipe-

line complete, and no new DMA requests are made. This

does not affect FIFO status.

0

9

PPTRAN

Parallel Port Transmit/Receive Select.

Indicates if the

processor is reading from external memory if cleared, (= 0)

or writing to external memory if set, (= 1).

0

Содержание ADSP-21261 SHARC

Страница 30: ...Contents xxx ADSP 2126x SHARC Processor Hardware Reference ...

Страница 40: ...Register Diagram Conventions xl ADSP 2126x SHARC Processor Hardware Reference ...

Страница 58: ...Differences From Previous SHARCs 1 18 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 112: ...Secondary Processing Element PEy 2 54 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 178: ...Summary 3 66 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 204: ...DAG Instruction Summary 4 26 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 322: ...Setting Up DMA 7 32 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 436: ...SPORT Programming Examples 9 86 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 521: ...ADSP 2126x SHARC Processor Hardware Reference 11 31 Input Data Port rts IDP_ISR end ...

Страница 522: ...Input Data Port Programming Example 11 32 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 590: ...Timer Programming Examples 14 20 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 796: ...I O Processor Registers A 174 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 800: ...B 4 ADSP 2126x SHARC Processor Core Manual ...

Страница 846: ...Index I 36 ADSP 2126x SHARC Processor Hardware Reference ...