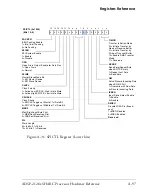

I/O Processor Registers

A-100

ADSP-2126x SHARC Processor Hardware Reference

Shift Registers

The processor core contains two separate 32-bit shift registers—one for

reception (

RXSR

) and one for transmission (

TXSR

).

Receive Shift Register (RXSR)

The

RXSR

register is clocked on the sampling edge of the

SPICLK

clock. The

active edge is the opposite edge from the sampling edge. The

RXSR

register

behaves the same way whether the device is in Slave or Master mode.

The register is configured by the

MSBF

and

WL

bits of the

SPICTL

register.

The

MSBF

bit indicates the data format (LSB-first or MSB-first) and selects

the direction of the shift. The

WL

bit indicates the length of the transfer—

8 bits if

WL

= 00, 16 bits if

WL

= 01, and 32 bits if

WL

= 10.

mation, see “SPI Control Register (SPICTL)” on page A-96.

Transmit Shift Register (TXSR)

The

TXSR

register is clocked on the active or shifting edge. The active edge

is the opposite edge from the sampling edge. The

TXSR

register can be

shifted right or left, depending on the direction of the data flow. This reg-

ister can also be loaded from the

TXSPI

register with data that is to be

transmitted.

This register behaves the same way whether the device is in Slave or Mas-

ter mode. The

TXSR

register contains 32 shift cells.

Each Shift register is configured by the

MSBF

and

WL

bits of the

SPICTL

reg-

ister. The

MSBF

bit indicates the data format (LSB-first or MSB-first) and

selects the direction of the shift. The

WL

bit indicates the length of the

transfer—8 bits if

WL

= 00, 16 bits if

WL

= 01, and 32 bits if

WL

= 10. When

WL

= 00, the upper 24 MSBs of the register loads with zeroes after a write

to the

TXSPI

register.

Содержание ADSP-21261 SHARC

Страница 30: ...Contents xxx ADSP 2126x SHARC Processor Hardware Reference ...

Страница 40: ...Register Diagram Conventions xl ADSP 2126x SHARC Processor Hardware Reference ...

Страница 58: ...Differences From Previous SHARCs 1 18 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 112: ...Secondary Processing Element PEy 2 54 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 178: ...Summary 3 66 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 204: ...DAG Instruction Summary 4 26 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 322: ...Setting Up DMA 7 32 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 436: ...SPORT Programming Examples 9 86 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 521: ...ADSP 2126x SHARC Processor Hardware Reference 11 31 Input Data Port rts IDP_ISR end ...

Страница 522: ...Input Data Port Programming Example 11 32 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 590: ...Timer Programming Examples 14 20 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 796: ...I O Processor Registers A 174 ADSP 2126x SHARC Processor Hardware Reference ...

Страница 800: ...B 4 ADSP 2126x SHARC Processor Core Manual ...

Страница 846: ...Index I 36 ADSP 2126x SHARC Processor Hardware Reference ...