with the

IIR_FCR.FIFOE

bit, automatic flow control is also disabled regardless of any other settings.

When auto CTS is not implemented or disabled, the transmitter is unaffected by

cts_n

.†

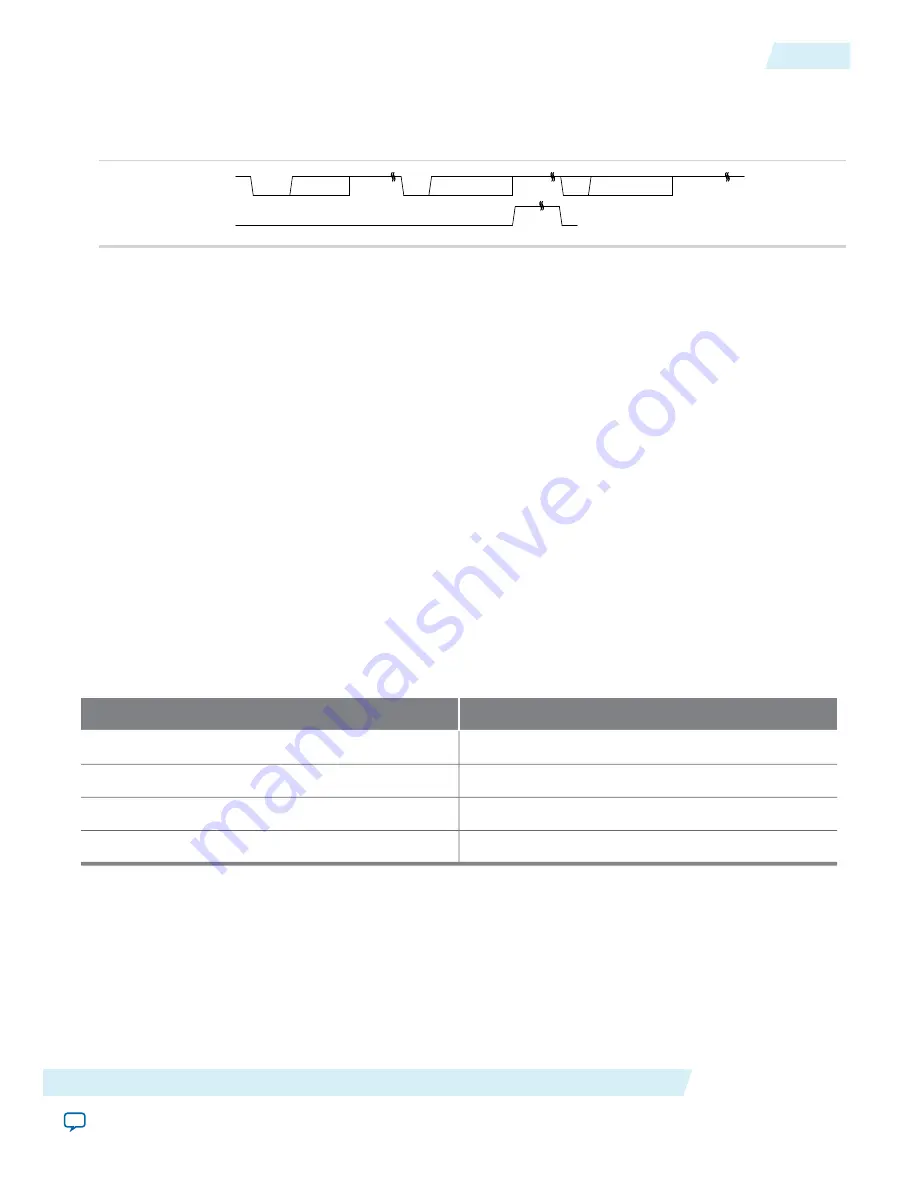

Figure 21-3: Automatic CTS Timing

sout

cts_n

start

data bits

stop

start

Disabled

data bits

stop

start

data bits

stop

Clocks

The UART controller is connected to the

l4_sp_clk

clock. The clock input is driven by the clock manager.

Related Information

on page 2-1

For more information, refer to the

Clock Manager

chapter.

Resets

The UART controller is connected to the

uart_rst_n

reset signal. The reset manager drives the signal

on a cold or warm reset.

Related Information

on page 3-1

For more information, refer to the

Reset Manager

chapter.

Interrupts

The assertion of the UART interrupt output signal occurs when one of the following interrupt types are

enabled and active: †

Table 21-2: Interrupt Types and Priority †

Priority

Interrupt Type

Highest

Receiver line status

Second

Received data available

Second

Character timeout indication

Third

Transmit holding register empty

You can enable the interrupt types with the interrupt enable register (

IER_DLH

).

Programmable THRE Interrupt

The UART has a programmable THRE interrupt mode to increase system performance. You enable the

programmable THRE interrupt mode with the interrupt enable register (

IER_DLH.PTIME

). When the

THRE mode is enabled, THRE interrupts and the

dma_tx_req

signal are active at and below a programmed

transmit FIFO buffer empty threshold level, as shown in the flowchart. †

Altera Corporation

UART Controller

21-5

Clocks

cv_54021

2013.12.30