ADM-VPX3-9Z2 User Manual

V1.1 - 16th January 2020

Signal

Frequency

FPGA Input

IO Standard

pin

VIDEO_REFCLK

27MHz

PS_MIO27 (Bank

501)

LVCMOS18

M21

Table 16 : VIDEO_REFCLK Connection

3.5.8 USB_REFCLK24M

The USB PHY and hub are provided with an independent 24.0MHz reference clock. This clock is asynchronous

to the clocks generated by the Si5338B and is not connected to the Zynq SoC.

3.5.9 ETH_CLK25M

The Ethernet PHYs are provided with an independant 25.0MHz reference clock. This clock is asynchronous to

the clocks generated by the Si5338B and is not connected to the Zynq SoC..

3.6 Resets

The Zynq PS can be reset via the two push button switches, SW1 and SW2.

Switch

Reset Type

Effect

SW1

Power on Reset

(PS_POR_B pin)

Clears all logic. Mode pins sampled (i.e. reconfigures hardware). Reboots

MPSoC.

SW2

Soft Reset

(PS_SRST_B pin)

Same as Power on Reset - but does not sample Mode pins (hardware

configuration unchanged).

Table 17 : Reset Switches

3.7 Zynq PS Block

3.7.1 Boot Modes

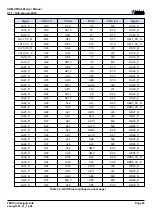

PS_MODE3

(SW4-4)

PS_MODE2

(SW4-3)

PS_MODE1

(SW4-2)

PS_MODE0

(SW4-1)

Boot Mode

ON

ON

ON

ON

JTAG

ON

ON

ON

OFF

Quad SPI (24 bit addressing)

ON

ON

OFF

ON

Quad SPI (32 bit addressing)

ON

ON

OFF

OFF

SD Flash - SD 2.0

ON

ON

ON

ON

eMMC v4.5 at 1.8V

Table 18 : Boot Mode Selection

Note: all other possible switch settings are reserved / invalid.

3.7.2 PS Memory Interfaces

The memory devices attached to the PS side of the MPSoC are outlined below.

3.7.2.1 Quad SPI Flash Memory

The ADM-VPX3-9Z2 has two Quad SPI Flash devices, up to 2Gb each. They can be interfaced seperately in x1,

x2,x4 modes or together in x8 mode.

Page 14

Functional Description

ad-ug-1323_v1_1.pdf