Chapter 5

Ladder Program Basics

5–11

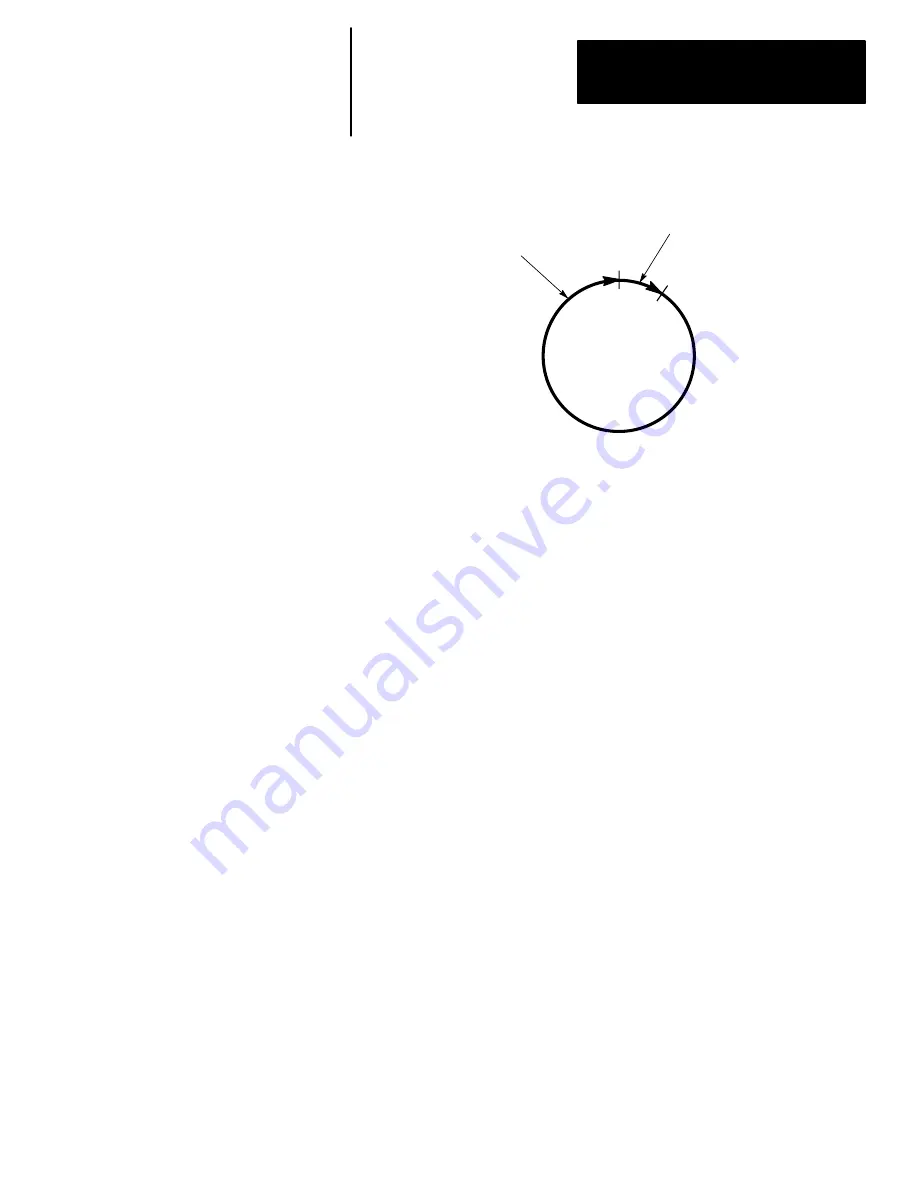

The diagram below shows a simplified operating cycle, consisting of the

program scan, discussed in the last section, and the I/O scan.

PROGRAM SCAN

I/O SCAN

In the I/O scan, data associated with external outputs is transferred from the

output data file to the output terminals. (This data was updated during the

preceding program scan.) In addition, input terminals are examined, and the

associated on/off state of the bits in the input data file are changed

accordingly.

In the program scan, the updated status of the external input devices is

applied to the user program. The processor executes the entire list of

instructions in ascending rung order. Status bits are updated according to

logical continuity rules as the program scan moves from instruction to

instruction through successive ladder rungs.

The I/O scan and program scan are separate, independent functions. Thus,

any status changes occurring in external input devices during the program

scan are not accounted for until the next I/O scan. Similarly, data changes

associated with external outputs are not transferred to the output terminals

until the next I/O scan.

Important: The description here does not account for the processor

overhead and communications portions of the operating cycle.

These are discussed in appendix D, Estimating Scan Time.

Operating Cycle (Simplified)