MC97F6108A User’s manual

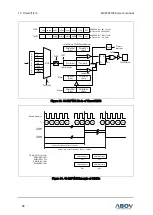

11. PPG (Programmable Pulse Generator)

95

11.1

PPG block diagram

P R E S C A L E R

÷

1

÷

4

÷

8

÷

16

÷

64

÷

2

5

6

÷

1

0

2

4

÷

2

0

4

8

PPGEN

3

PPGCK[2:0]

f

X

CMP3IF

CMP1IF

010

011

100

CAPE

-

-

PPGIN[2]

PPGIN[1]

PPGIN[0]

-

PPG_PE

-

PPGCR

PPGCR1

ADDRESS : E2

H

INITIAL VALUE : 0000_0000

b

ADDRESS : E3

H

INITIAL VALUE : 0000_0000

b

PPGEN

-

CAPE

PPGCK2

PPGCK1

PPGCK0

PPGCN

PPGST

PPGIF

TPPGOen

PPGMD

DETC3EN

DETC1EN

-

-

PPGCR2

ADDRESS : E1

H

INITIAL VALUE : 0000_0000

b

PPGH/L (16-bit Counter)

PPGST

PPGIF

PPG Interrupt

DUTY Compare

REGISTER

C

le

a

r

&

S

ta

rt

PERIOD Compare

REGISTER

PPGDH/L (16-bit)

S

R

Q

clear

PPG_PE

PPGO

PPG Period Register

~(DUTY state)

PPGPH/L or PPGPXH/L

(16-bit)

PPG Non-operating state

PPG Duty Register

PPGCH/L (16bit)

PPG Capture Register

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

C0_FLAG

PPGMD

PPGIN[2:0]

3

clear

DETC3EN

clear

DETC1EN

C1_FLAG

CMP4IF

PPGCLK

-

C3_FLAG

Figure 32. PPG Block Diagram