16. Inter Integrated Circuit (I2C)

MC97F6108A User’s manual

178

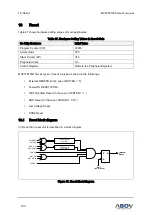

16.7.4

Slave receiver

I2C Block that is under IIC enable and INTEN enable on I2CMR is monitoring I2C bus lines for being a

start condition and self-address with I2CSAD. To have both signals of start signal and getting self-

address, I2C block generate I2C interrupt with the status bits (SSEL, BUSY RXACK, SLAVE mode ...)

after sending ACK signal. At the time I2C block control SCL line to low state for ready to get/handle

next i2c data. If I2C block by I2C interrupt service is ready for next step, it is to release the SCL line to

high state for getting next SCL clock from the master. I2C Block decide bus direction (data

receive/transmission) by data direction (R/

W̅

) bit in Slave address from master. The state of bus

direction is on TMOD bit on I2CSR register. If the master generate Stop condition I2C block receive

STOP condition and generate I2C interrupt. I2C interrupt service write any data to I2CSR and finish

Slave operation.

Example code of slave mode is introduced in the followings:

I2C Interrupt service

I2C Slave service

if(Getting SSEL and send ACK) // received Self-address form master

if(TMODE)

// data direction (R/

W̅

)

I2CDR=I2C_TXData

// Transmission mode, Load data

else

I2C_RXData =I2CDR

else

if (Get STOP condition)

else

if (TMODE)

// data direction (R/

W̅

)

I2CDR= I2C_TXData

// Transmission mode, Load data

else

I2C_RXData =I2CDR

// Save received Data

I2CSR=0xff;