16. Inter Integrated Circuit (I2C)

MC97F6108A User’s manual

172

16.6

Synchronization/ arbitration

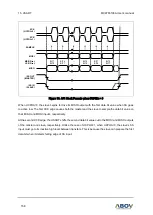

Clock synchronization is performed using the wired-AND connection of I2C interfaces to the SCL line.

This means that a HIGH to LOW transition on the SCL line will cause the devices concerned to start

counting off their LOW period and it will hold the SCL line in that state until the clock HIGH state is

reached. However the LOW to HIGH transition of this clock may not change the state of the SCL line if

another clock is still within its LOW period. In this way, a synchronized SCL clock is generated with its

LOW period determined by the device with the longest clock LOW period, and its HIGH period

determined by the one with the shortest clock HIGH period.

A master may start a transfer only if the bus is free. Two or more masters may generate a START

condition. Arbitration takes place on the SDA line, while the SCL line is at the HIGH level, in such a way

that the master which transmits a HIGH level, while another master is transmitting a LOW level will

switch off its DATA output state because the level on the bus doesn’t correspond to its own level.

Arbitration continues for many bits until a winning master gets the ownership of I2C bus. Its first stage

is comparison of the address bits.

Figure 80. Clock Synchronization during Arbitration Procedure

Figure 81. Arbitration Procedure of Two Masters

High Counter Reset

Fast Device SCLOUT

Slow Device SCLOUT

SCL

Wait High

Counting

Start High

Counting

Device1

Data Out

SCL on BUS

Device2

Data Out

SDA on BUS

S

Arbitration Process

not adapted

Device 1 loses

Arbitration

Device1 outputs

High