A96G140/A96G148/A96A148 User’s manual

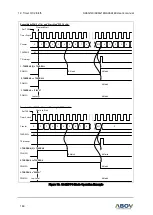

13. Buzzer driver

151

Table 27. Buzzer Driver Register Map

Name

Address

Direction

Default

Description

BUZDR

8FH

R/W

FFH

Buzzer Data Register

BUZCR

97H

R/W

00H

Buzzer Control Register

13.3

Register description

BUZDR (Buzzer Data Register): 8FH

7

6

5

4

3

2

1

0

BUZDR7

BUZDR6

BUZDR5

BUZDR4

BUZDR3

BUZDR2

BUZDR1

BUZDR0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value: FFH

BUZDR[7:0]

This bits control the Buzzer frequency

Its resolution is 00H ~ FFH

BUZCR (Buzzer Control Register): 97H

7

6

5

4

3

2

1

0

–

–

–

–

–

BUCK1

BUCK0

BUZEN

–

–

–

–

–

R/W

R/W

R/W

Initial value: 00H

BUCK[1:0]

Buzzer Driver Source Clock Selection

BUCK1

BUCK0

Description

0

0

fx/32

0

1

fx/64

1

0

fx/128

1

1

fx/256

BUZEN

Buzzer Driver Operation Control

0

Buzzer Driver disable

1

Buzzer Driver enable

NOTE:

fx: System clock oscillation frequency.