Document number

205065

Version

Rev. N

Issue date

2019-02-04

Sirius OBC and TCM User Manual

Page

145

of

174

8. System-on-Chip definitions

In this section the peripherals, memory sections and interrupts defined for the SoC for the

Sirius OBC and Sirius TCM are described

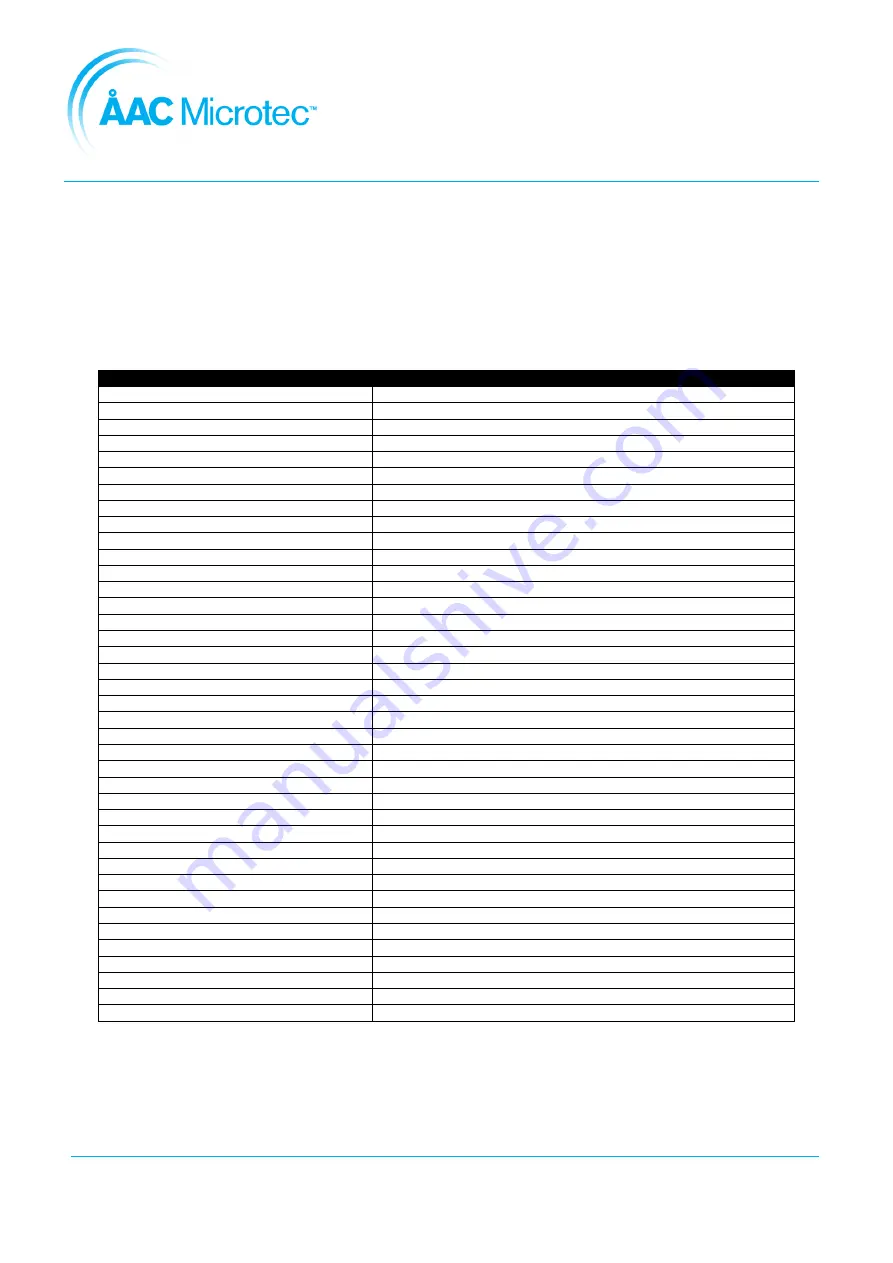

8.1. Memory mapping

Table 8-1 - Sirius memory structure definition

Memory Base Address

Function

0xF0000000

Boot ROM

0xE0000000

CCSDS (Sirius TCM only)

0xCB000000

Watchdog

0xCA000000

SpaceCraft Elapsed Time

0xC1000000

SoC info

0xC0000000

Error Manager

0xBD000000 - 0xBF000000

Reserved

0xBC000000

Reserved for SPI interface 1

0xBB000000

Reserved for SPI interface 0

0xBA000000

GPIO

0xB6000000

Reserved for ADC controller 1

0xB5000000

ADC controller 0

0xB4000000

Reserved

0xB3000000

Mass memory flash controller (Sirius TCM only)

0xB2000000

System flash controller

0xB1000000

Reserved

0xB0000000

NVRAM controller

0xAC000000

Reserved for PCIe

0xAB000000

Reserved for CAN

0xAA000000

Reserved for USB

0xA9000000 -0xA3000000

Reserved

0xA2000000

Reserved for redundant SpaceWire

0xA1000000

SpaceWire

0xA0000000

Reserved for Ethernet MAC

0x9C000000 -0x9F000000

Reserved

0x9B000000

Reserved for I2C interface 1

0x9A000000

Reserved for I2C interface 0

0x99000000

Reserved

0x98000000

UART 7 (Safe bus functionality, RS485)

0x97000000

UART 6 (PSU control functionality, RS485)

0x96000000

UART 5

0x95000000

UART 4 (Routed to LVDS HK on Sirius TCM)

0x94000000

UART 3 (Routed to RS422 HK on Sirius TCM)

0x93000000

UART 2

0x92000000

UART 1

0x91000000

UART 0

0x90000000

UART Debug (LVTTL)

0x80000000 - 0x8F000000

Reserved for customer IP

0x00000000

SDRAM memory including EDAC (64 MB)