Summary of Contents for FHB5-PE1MWB04-00

Page 1: ...Document No F T MU S2PCIENF A 0 A3 SL100 SL240 Multi Channel PCIe User Guide FibreXtreme ...

Page 2: ......

Page 6: ......

Page 7: ...SL100 SL240 1 FOREWORD ...

Page 8: ......

Page 11: ...SL100 SL240 2 INTRODUCTION ...

Page 12: ......

Page 16: ......

Page 17: ...SL100 SL240 3 TECHNICAL SUPPORT ...

Page 18: ......

Page 20: ......

Page 21: ...SL100 SL240 4 PRODUCT OVERVIEW ...

Page 22: ......

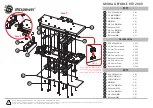

Page 31: ...SL100 SL240 5 INSTALLATION ...

Page 32: ......

Page 37: ...SL100 SL240 6 OPERATION ...

Page 38: ......

Page 43: ...SL100 SL240 7 APPENDIX A ...

Page 44: ......

Page 47: ...SL100 SL240 8 APPENDIX B ...

Page 48: ......

Page 54: ......

Page 55: ...SL100 SL240 9 APPENDIX C ...

Page 56: ......

Page 59: ...SL100 SL240 10 APPENDIX D ...

Page 60: ......

Page 70: ......