Cirrus Logic Confidential

Copyright

Cirrus Logic, Inc. 2009–2015

(All Rights Reserved)

http://www.cirrus.com

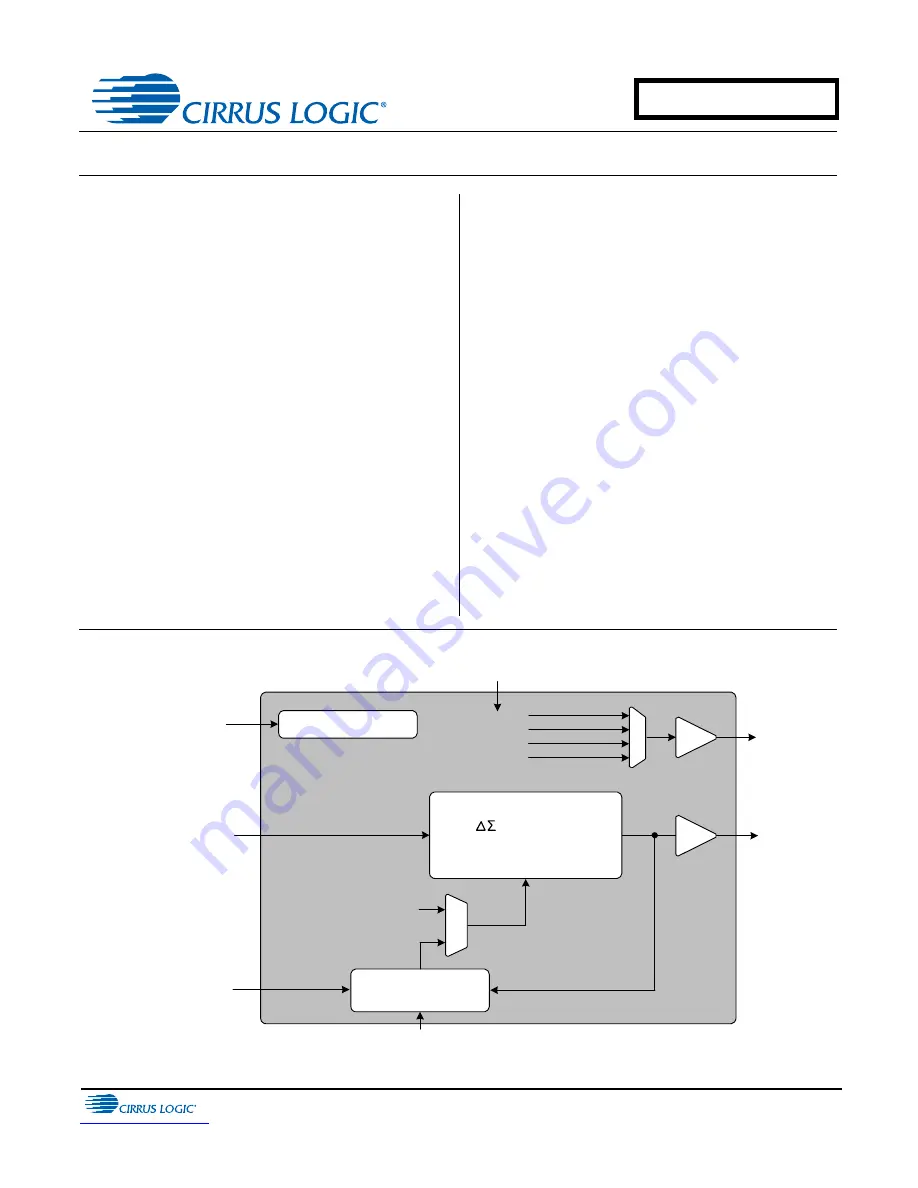

Fractional-N Clock Synthesizer & Clock Multiplier

Delta-Sigma Fractional-N Frequency Synthesis

– Generates a Low Jitter 6 - 75 MHz Clock

from an 8 - 75 MHz Reference Clock

Clock Multiplier / Jitter Reduction

– Generates a Low Jitter 6 - 75 MHz Clock

from a Jittery 50 Hz to 30 MHz Clock

Highly Accurate PLL Multiplication Factor

– Maximum Error Less Than 1 PPM in High-

– Configurable Hardware Control Pins

– Configurable Auxiliary Output

Flexible Sourcing of Reference Clock

– External Oscillator or Clock Source

– Supports Inexpensive Local Crystal

– No External Analog Loop-filter

OCT '15

DS758F3

CS2000-OTP