CDB43198-GBK

CDB43198-GBK Kit Manual

Copyright ©

2018 Cirrus Logic, Inc. and

Cirrus Logic International Semiconductor Ltd.

All rights reserved.

DS1156DB1

AUG '18

Features

•

Configurable serial audio headers for PCM, DSD and DoP audio

•

Headphone and line outputs

•

Analog and S/PDIF audio input

•

USB audio module capability

•

WISCE™ I

2

C-based software control

•

Windows® compatible

Description

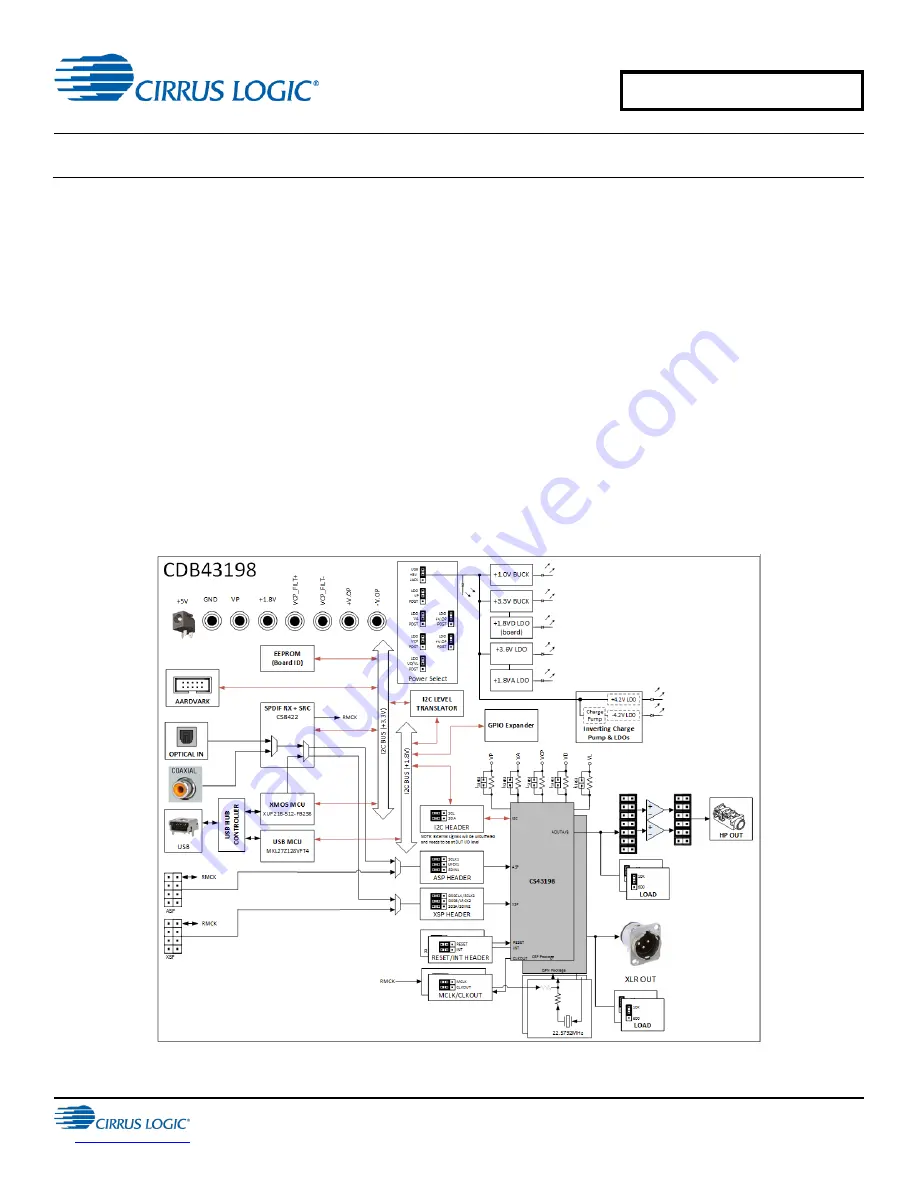

The CDB43198-GBK is a dedicated platform for testing and evaluating the CS43198. The CS43198 is a high-performance

audio DAC with integrated impedance detection and headphone drivers. To allow comprehensive testing and evaluation

of the performance of the CS43198, extensive software-configurable options are available through the CDB43198

evaluation kit. The kit also included the CDB-HDR-MEAS, for measuring the 130 dB dynamic range performance of the

CS43198.

Software options, such as register settings for the CS43198, are configured via the WISCE software tool, which

communicates with the CDB43198-GBK via an Aardvark I

2

C/SPI host adapter from a Windows computer, or via Mini-USB

cable.

Figure 1 CDB43198 Board Block Diagram