A

1

2

3

4

5

6

7

8

9

10

B

C

D

E

F

G

H

I

J

K

L

M

N

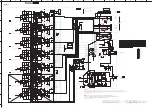

RX-V475/HTR-4066/RX-V500D

104

DIGITAL 2/5

★

All voltages are measured with a 10MΩ/V DC electronic voltmeter.

★

Components having special characteristics are marked

⚠

and must be replaced

with parts having specifications equal to those originally installed.

★

Schematic diagram is subject to change without notice.

● 電圧は、内部抵抗 10MΩの電圧計で測定したものです。

● ⚠印のある部品は、安全性確保部品を示しています。部品の交換が必要な場合、

パーツリストに記載されている部品を使用してください。

● 本回路図は標準回路図です。改良のため予告なく変更することがあります。

3.3

3.3

5.5

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.2

3.2

0

0

0

3.3

0

0

0

2.9

2.7

2.6

0

3.3

3.3

3.3

3.3

0

0

0

5.2

3.3

-0.3

0

0

3.3

3.3

3.5

3.5

1.5

3.3

3.3

5.2

-0.1

-0.2

1.5

0.9

0.6

2.9

3.2

2.6

2.6

2.7

0.7

-0.2

0.6

3.2

3.3

3.3

3.3

2.9

3.1

3.3

-0.3

0

E 8 A _ T X D

DC_PRT

DSP_FMT

HPRY

EX_SCK

HDMI_MUTE

DIR_WCK

DSP_N_INT

N_FCT

S P R Y _ 5 C H

EEP_N_CS

DSP_N_INT

EEP_MISO

TUN_N_RST

KEY1

USB_BUSY

HDMI_SCL

DSP_N_CS

VOL_RA

H P R Y

T H M 2 _ P R T

C N V S S

HDMI_N_RST

HDMI_PON

AMP_LMT

S P R Y _ S B _ B A

FPGA_MISO

E 8 A _ N _ C E

NCPU_SPI_MISO

V O L _ M O S I

M T _ N _ 5 C H

DIR_N_CS

HDMI_N_INT

AMP_OLV

TUN_N_RST

REM_IN

HDMI_CEC

L M T _ I

D C _ P R T

NCPU_VBUSDRV

HDMI_SDA

E 8 A _ S C L K

DIR_N_INT

E 8 A _ N _ C E

K E Y 2

DSP_MOSI

DSP_N_RST

DSP_SCK

E 8 A _ N _ E P M

D A C _ N _ C S

N C P U _ A M U T E

T U N _ S C L

E 8 A _ N _ E P M

T U N _ S D A

DSP_N_CS

KEY2

DSP_N_RDY

DIR_SDO

I_PRT

T H M 1 _ P R T

DSP_MOSI

E 8 A _ R X D

K E Y 1

L M T _ D C

N _ F C T

HDMI_CEC

TUN_N_INT

M T _ S B

EX_SCK

A M P _ O L V

T R A N S _ R Y

DSP_MISO

V O L _ S C K

M T _ 5 C H

DSP_FMT

MIC_N_DET

DSP_N_RDY

DIR_N_INT

FLD_N_RST

FLD_N_CS

HDMI_PON

DIR_N_RST

HDMI_N_INT

DSP_MISO

SPRY_5CH

TUN_SCL

MT_SB

TRANS_RY

E 8 A _ B U S Y

AMP_LMT

P R Y

C N V S S

HDMI_MUTE

E 8 A _ B U S Y

VOL_RB

MIC_N_DET

HP_N_DET

DSP_N_RST

EX_MOSI

TUN_SDA

I _ P R T

VOL_RB

H P _ N _ D E T

REM_IN

EEP_N_CS

L M T _ P S 1

E 8 A _ S C L K

T H M 3 _ P R T

DAC_N_CS

V I D I 2 C _ O N

M T _ N _ S W

PSW_N_DET

PSW_N_DET

TUN_N_INT

U S B _ V B U S _ P R T

DSP_SCK

M T _ S W

SPRY_SB_BA

VOL_RA

VOL_SCK

VOL_MOSI

DIR_N_RST

DIR_N_CS

NCPU_SPI_REQ

NCPU_SPI_RDY

D C D C _ P O N

U S B _ V B U S _ P O N

STBY_LED

NCPU_PON

DSP_PON

+3.3S_PON

NCPU_SPI_SCK

N C P U _ S P I _ N _ C S

N C P U _ N _ R S T

D I R _ S D O

D I R _ W C K

L M T _ 0 L V

L M T _ P S 2

THM1_PRT

THM2_PRT

VID_PON

PS2_PRT

PS1_PRT

DEST

CPU_N_RSTCPU_N_RST

ACPWR_DET

VID_PON

VID_PON

M T _ N _ S B

OSDFS_BUS_SEL

OSDFS_N_CS

FPGA_MOSI

FPGA_SCK

FPGA_MISO

NCPU_VBUSDRV

NCPU_SPI_MOSI

NCPU_SPI_MISO

NCPU_AMUTE

NCPU_SPI_SCK

NCPU_SPI_N_CS

NCPU_N_RST

NCPU_PON

NCPU_SPI_REQ

NCPU_SPI_RDY

DCDC_PON

USB_VBUS_PON

DSP_PON

E X _ M O S I

E X _ S C K

I_PRT

USB_VBUS_PRT

L M T _ I

L M T _ P S 3

L M T _ 0 L V

O S D F S _ N _ C S

HDMI_N_RST

MHL_WAKE

OSDFS_BUS_SELOSDFS_BUS_SEL

NDAC_N_MT

NDAC_N_MT

P S 2 _ P R T

P S 1 _ P R T

P S 1 _ P R T

P S 3 _ P R T

P S 3 _ P R T

EX_MOSI

L M T _ P S 1

L M T _ P S 2

L M T _ P S 3

H D M I _ S D A

H D M I _ S C L

FPGA_MOSI

FPGA_SCK

NCPU_SPI_MOSI

EEP_MISO

MT_SW

MT_5CH

STBY_LED

FLD_N_RST

FLD_N_CS

+3.3S_PON

HDMI_SCL

HDMI_SDA

VIDI2C_ON

L3_DET

PSW_N_DET

CPU_N_RST

ACPWR_DET

D E S T

L M T _ D C

DRCT_LED

IN_RD

PWM_PDN

PWM_N_RST

DAB_PON

DAB_PON

DRCT_LED

P D S W

Z 2 _ L E D

REM_OUT

IN_RC

T U N I 2 C _ O N

M H L _ C D _ I N 5

M H L _ V B U S _ N _ P R T

M H L _ V B U S _ P O N

MHL_CD_IN5

MHL_VBUS_PON

MHL_VBUS_N_PRT

+5EX_PON

PWM_PDN

PWM_N_RST

IN_RC

PS1_PRT

PDSW

MODE

E 8 A _ T X D

HDMI_SCL

HDMI_SDA

FLD_SCK

FLD_MOSI

IN_RD

Z2_LED

E 8 A _ R X D

PS2_PRT

L 3 _ D E T

P S 2 _ P R T

P S 2 _ P R T

THM3_PRT

+5EX_PON

SEL_NDAC

S E L _ N D A C

1 0 K

R 2 1 6

D G N D

D G N D

DGND

C229

0.01/16(B)

22

R243

1 0 K

R 2 1 8

T U E

22

R241

4 . 7 K

R 2 7 2

4 . 7 K

R 2 0 9

100K

R268

PL0.3

C 2 5 0

n o _ u s e

PL0.3

C B 2 7

5 2 0 4 5

1

2

3

4

5

6

7

8

9

R203

1K

FPGA_SCK

PL3.0

R250

10K

HDMI_N_RST

D G N D

D G N D

1 0 0 P ( C H )

C 2 6 1

C 2 0 8

n o _ u s e

HDMI_N_INT

DGND

DIR_N_CS

D G N D

4 7 0

R 2 7 6

5 6 K

R 2 5 3

C 2 0 5

n o _ u s e

22

R279

D G N D

D G N D

D G N D

1 / 1 0

C 2 4 5

C224

0.01/16(B)

D G N D

C 2 0 4

n o _ u s e

100P(CH)

C256

1 K

R 2 2 6

HDMI_CEC

PL3.0

C 2 0 6

n o _ u s e

C 2 5 3

n o _ u s e

A 1 5 7 6 U B T L R

Q 2 0 8

C 2 5 2

n o _ u s e

C 2 5 1

n o _ u s e

D G N D

PL3.0

D G N D

R205

no_use

C 2 6 3

n o _ u s e

10K

R245

R202

9.1K

R 2 7 5

4 7 0

8 M H Z

X L 2 1

1

2

3

C220

0.01/16(B)

0.1/10(BJ)

C248

DSP_N_RDY

DSP_MISO

0

R239

C227

0.01/16(B)

HDMI_SDA

10K

R248

D G N D

D G N D

100

R277

C 2 1 1

n o _ u s e

C 2 3 8

n o _ u s e

1 K

R 2 5 1

T P 1 0 5 0

C 2 4 0

n o _ u s e

C 2 5 7

n o _ u s e

Q 2 0 3

H N 4 B 0 1 J E ( T E 8 5 L ,

B 1

E

B 2

C 2

C 1

1 0 0 P ( C H )

C 2 6 4

C217

0.1/10(BJ)

C 2 1 0

n o _ u s e

R247

47

C 2 2 3

n o _ u s e

C 3 0 1

3 3 / 1 0

100

R280

C 2 6 2

n o _ u s e

C 2 0 7

n o _ u s e

D G N D

D G N D

10K

R214

C 2 5 4

n o _ u s e

C 2 3 9

n o _ u s e

OSDFS_N_CS

D G N D

D G N D

C201

no_use

DIR_N_INT

R213

no_use

DGND

DSP_FMT

DGND

DGND

R 2 3 5

1 0 0 K

DIR_N_RST

1 0 0

R 2 6 6

DSP_N_RST

C 2 4 1

n o _ u s e

D G N D

FPGA_MOSI

D G N D

R201

1K

C259

1/25

C 2 3 6

n o _ u s e

R246

100

10K

R204

C 2 2 2

n o _ u s e

C 3 0 2

3 3 / 1 0

OSDFS_BUS_SEL

DIR_WCK

D G N D

R 2 7 4

4 7 0

R 2 6 2

1 K

PL3.0

DGND

C 2 5 5

0 . 0 1 / 1 6 ( B )

Q 2 0 5

A 1 5 7 6 U B T L R

R252

10K

C216

0.1/10(BJ)

100

R244

DGND

4 . 7 K

R 2 7 3

3 3 K

R 2 0 8

NCPU_VBUSDRV

L 1 0 1

B K P 1 0 0 5 H S 6 8 0 - T

DSP_N_INT

R215

no_use

C226

0.01/16(B)

D G N D

DIR_SDO

C228

0.01/16(B)

D G N D

C215

0.1/10(BJ)

A 1 5 7 6 U B T L R

Q 2 0 9

R 2 6 3

n o _ u s e

100K

R270

T P 1 0 5 1

C 2 4 2

n o _ u s e

C 2 1 4

0 . 1 / 1 0 ( B J )

PL0.3

J 2 0 3

n o _ u s e

A 1 5 7 6 U B T L R

Q 2 1 0

D G N D

1 K

R 2 2 8

DSP_N_CS

C225

0.01/16(B)

C 2 4 3

n o _ u s e

C260

1/25

C258

1/25

DSP_MOSI

D G N D

4 7 K

R 2 6 4

FPGA_MISO

10K

R212

C 2 3 7

n o _ u s e

4 7 K

R 2 6 5

R 2 2 2

4 7

A G N D

R249

10K

C218

0.01/16(B)

DAC_N_CS

100K

R269

10K

R237

0.1/10(BJ)

C247

0 . 1 / 1 0 ( B J )

C 2 4 6

D G N D

Q 2 0 1

H N 4 B 0 1 J E ( T E 8 5 L ,

B 1

E

B 2

C 2

C 1

CB26

5 2 0 4 4

V Q 0 4 4 4 0

1

2

3

4

5

6

7

8

9

C 2 3 5

n o _ u s e

HDMI_PON

DSP_SCK

HDMI_SCL

C 2 4 4

n o _ u s e

C 2 0 9

n o _ u s e

4 . 7 K

R 2 7 1

R242

47

D G N D

22

R278

HDMI_MUTE

D G N D

CB22

52044

C 2 0 3

n o _ u s e

C 2 0 2

n o _ u s e

T P 1 1 0 0

D G N D

T P 1 0 8 8

C269

4.7/6.3

+ 3 . 3 M

C267

4.7/6.3

R P 1 3 0 Q 3 3 1 D - T R - F

Y C 2 8 8 A 0

VDD

GND

VOUT

CE/CE

+ 5 . 5 V

R P 1 3 0 Q 3 3 1 D - T R - F

Y C 2 8 8 A 0

VDD

GND

VOUT

CE/CE

+ 3 . 3 S

C268

1/25

C266

1/25

D G N D

C 2 4 9

n o _ u s e

1 K

R 2 2 9

1 K

R 2 2 3

PL0.3

DGND

Q 2 0 2

H N 4 B 0 1 J E ( T E 8 5 L ,

B 1

E

B 2

C 2

C 1

PL3.0

NCPU_AMUTE

+ 3 . 3 M

+ 3 . 3 M

+ 3 . 3 S

+3.3S

+ 3 . 3 S

+3.3S

+3.3S

+3.3S

+ 3 . 3 M

+ 3 . 3 M

+ 3 . 3 M

+ 3 . 3 M

+ 3 . 3 M

+ 3 . 3 M

+ 3 . 3 H

+ 3 . 3 D S P

+ 3 . 3 M

+ 3 . 3 S

+ 3 . 3 S

+ 3 . 3 S

+ 3 . 3 M

+ 3 . 3 M

+ 3 . 3 M

+ 3 . 3 S

+5T

+3.3M

+3.3DSP

DGND

+3.3M

DGND

+3.3S

NCPU_SPI_MOSI

NCPU_SPI_MISO

NCPU_SPI_SCK

NCPU_SPI_N_CS

NCPU_N_RST

NCPU_PON

NCPU_SPI_RDY

NCPU_SPI_REQ

DCDC_PON

USB_VBUS_PON

DSP_PON

+ 3 . 3 S

D G N D

+3.3S

A1576UBTLR

Q207

330

R267

USB_VBUS_PRT

Q 2 0 6

A 1 5 7 6 U B T L R

DGND

PL3.0

Q 2 0 4

C 4 0 8 1 U B T L R

PL0.3

+3.3S

TUR

TUL

10K

R282

DGND

10K

R240

NDAC_N_MT

+ 5 A

12K

R210

D G N D

R211

no_use

+ 5 . 5 V

18K

R206

D G N D

10K

R207

C 2 1 3

n o _ u s e

C 2 1 2

n o _ u s e

C219

0.1/10(BJ)

22

R238

2 2

R 2 1 7

C230

0.01/16(B)

C231

0.01/16(B)

C232

0.01/16(B)

C233

0.01/16(B)

2 2

R 2 5 9

2 2

R 2 6 1

22

R260

22

R255

22

R236

CB24

52151

P N 2 1

R351

100X4

R352

100X4

R353

100X4

1

2

4

5

7

8

3

6

R354

100X4

R355

100X4

R219

100

+ 3 . 3 M

R927

10K

R 9 1 8

n o _ u s e

D G N D

D G N D

UPA672T-T1-A

Q902

G

2

D

6

S

1

R 9 1 9

n o _ u s e

G

5

D

3

S

4

CB91

52044

+3.3D

C B 2 8

n o _ u s e

I C 2 7

D 2 0 4

1 S S 3 5 5 V M

C 2 7 2

1 0 / 6 . 3

I C 2 7

S N 7 4 L V C 1 G 1 7 D C K R

2

I C 2 7

+ 3 . 3 M

C271

0.1/10(BJ)

D 2 0 1

R B 5 2 1 S - 3 0 T E 6 1

+ 3 . 3 M

R234

470K

R 2 3 3

1 M

D G N D

C B 2 9

P H I

D205

1SS355VM

+ 5 . 5 V

DGND

Q 2 1 1

H N 4 B 0 1 J E ( T E 8 5 L ,

B 1

E

B 2

C 2

C 1

+3.3M

DGND

+ 3 . 3 T

L 2 0 1

n o _ u s e

I C 2 6

I C 2 6

T C 7 W H 1 2 6 F K

6

I C 2 6

T C 7 W H 1 2 6 F K

3

+ 3 . 3 D S P

CB21

5 2 0 4 4

R356

100X4

1

2

4

5

7

8

3

6

1 0 0 0 P ( B )

C 2 6 5

1 0 0 0 P ( B )

C 2 3 4

1 0 0 0 P ( B )

C 2 2 1

I C 2 2

R 1 E X 2 5 0 3 2 A T A 0 0 A

S

Q

W

V S S

D

C

H O L D

V C C

R 3 5 9

1 0 K X 4

R 3 5 7

1 0 0 X 4

R 3 5 8

1 0 0 X 4

R220

1K

R224

1K

R221

9.1K

D G N D

+ 3 . 3 M

R 3 6 2

4 7 X 4

R 3 6 3

4 7 X 4

DAB_PON

R364

100X4

C 2 7 0

n o _ u s e

C 2 7 3

n o _ u s e

C 2 7 4

n o _ u s e

C 2 7 5

n o _ u s e

MHL_VBUS_N_PRT

MHL_CD_IN5

MHL_VBUS_PON

+5EX_PON

CB2

5

52151

0

J206

J205

no_use

+ 3 . 3 S

R225

10K

D G N D

P L 0 . 3 M

P L 3 . 0 M

C 2 7 6

n o _ u s e

D G N D

R227

no_use

DAB_SPDIF

J207

no_use

0

J208

R 3 6 1

1 0 0 K X 4

R 3 6 0

1 0 0 K X 4

PS2_PRT

CB23

no_use

10K

R230

+ 3 . 3 M

SEL_NDAC

R 2 3 1

n o _ u s e

P14_0

T X D

D G N D

BYTE

C N V s s

A N 0 _ 2

C L K 1

N_INT0

N_INT1

P3_2

A N 0 _ 0

S C L 0

N_INT2

P 1 1 _ 3

E E P R O M

I C / C B / X L : 2 1 - 4 0

A r r a y R : 3 5 1 - 4 0 0

C h e m i . C : 3 0 1 - 4 0 0

O H T E R : 2 0 1 - 4 0 0

SDA2

P 6 _ 0

P12_2

S C L K

TXD7

P 1 3 _ 7

/ R E S

P 1 _ 0

P4_4

t o 0 0 1 . s h t

( H D M I )

P 5 _ 4

P 1 2 _ 7

CLK4

SIN4

D I G I T A L 2 : C P U

P 1 3 - 6

V S S

P2_0

P4_2

N_INT7

P1_1

SCL2

( 2 1 2 5 )

P3_7

RXD1

TA2IN

VSS

P 6 _ 4

P12_4

A N 0 _ 4

P1_4

P4_1

RXD7

VCC1

CEC

S D A 0

SOUT3

P 1 3 _ 2

VCC1

P4_0

A N 0

SIN3

TXD1

VREF

A N 5

C L K 0

TA4IN

P8_6

A V S S

P 5 _ 5

TXD6

( 1 6 0 8

0 . 5 % )

P 1 3 _ 1

P 1 3 _ 4

P 1 1 _ 5

P2_3

M U T E

S B L \ S B R

P 1 3 _ 3

P7_2

P 1 1 _ 2

P7_7

CLK7

P 0 _ 7

B U S Y

VCC2

A N 0 _ 5

t o O P E ( 1 )

P2_1

P4_3

P 5 _ 7

Destination

P 1 1 _ 7

P 5 _ 6

A N 1

P 1 3 - 5

TA1IN

A N 2

P 5 _ 0

P 1 1 _ 6

A N 7

P 1 2 _ 6

P14_1

P7_6

P 1 1 _ 1

N_INT3

P7_4

AVCC

P1_7

P3_0

P 5 _ 1

P 1 1 _ 0

P 1 3 _ 0

B

A N 0 _ 1

P1_6

A N 4

N_INT6

P3_3

( 3 2 k b i t s )

A N 3

RXD6

P8_0

P2_7

P3_1

A N 6

P2_6

P2_2

P 1 2 _ 5

M U T E

L / C / R / S L / S R

VSS

SOUT4

CLK3

A

XIN

P 5 _ 2

XOUT

P9_4

A N 0 _ 3

/ E P M

P12_1

t o 0 0 3 . s h t

( D S P )

P3_5

/ C E

P 1 1 _ 4

CNVSS

/RESET

FCT

P12_3

N C

DA0

P 0 _ 6

P3_4

+ 5 D

M U T E

S u b W o o f e r

t o 0 0 4 . s h t

( D I R & P S )

P12_0

P8_7

P 5 _ 3

P3_6

R X D

DGND

FLD_MOSI

FLD_SCK

STBY_LED

KEY1

REM_IN

FLD_N_RST

+3.3M

MIC_N_DET/REC_SEL

PSW_N_DET

KEY2

VOL_RB

+3.3DSP

VOL_RA

FLD_N_CS

+5T

PS1_PRT

PS2_PRT

VID_PON

R_200_DET

t o O P E ( 4 )

CPU_N_RST

+3.3M

PRY

ACPWR_DET

DGND

DEST

t o O P E ( 2 )

SCL

Rch

GND

SDA

TVCC

RST

Lch

GPIO2

+3.3S

THM2_PRT

DGND

THM1_PRT

M

3

.

3

+

S

3

.

3

+

THM3_PRT

SPRY_5CH

HPRY

MUTE_SW

PS1_PRT/PDSW

DC_PRT

I_PRT

VOL_MOSI

AMP_OLV

MUTE_5ch

SPRY_SB/SPRY_B

MUTE_SB/MUTE_Z2

VOL_SCK

HP_N_DET

TRANS_RY

AMP_LMT

DG

D I A G _ F C T

t o 0 0 5 . s h t

( N E T )

t o 0 0 1 . s h t

( H D M I )

PS Protection

t o 0 0 3 . s h t

t o 0 0 4 . s h t

( D S P & D A C )

AD_CVBS

AVID_SDA

VE

AVID_SCL

L3_DET

t o T U N E R P A C K

t o O P E ( 3 )

t o M A I N ( 1 )

I C / C B / X L : 9 1 - 9 9

A r r a y R : 9 4 1 - 9 9 9

O H T E R : 9 0 1 - 9 9 9

B R 2 5 S 3 2 0 F V T - W E 2

Y D 9 1 4 A 0

F o r c e R E S E T

IN_RD

DGND

PRY

+5.5V

f o r

F A T E S T

IN_RC

DRCT_LED

R 1 E X 2 5 0 3 2 A T A 0 0 A

Y E 1 8 2 A 0

t o 0 0 1 . s h t

( M H L )

Z2_LED

(2125)

A-side

to 004.sht

(DIR)

PWM_SCL

NET_RF

NET_RE

PWM_SDA

R E M A R K S

C A P A C I T O R

P A R T S

N A M E

N O

N O

M A R K

M A R K

E L E C T R O L Y T I C

C A P A C I T O R

C E R A M I C

C A P A C I T O R

P O L Y E S T E R F I L M

C A P A C I T O R

P O L Y S T Y R E N E

F I L M

C A P A C I T O R

M I C A

C A P A C I T O R

P O L Y P R O P Y L E N E

F I L M

C A P A C I T O R

S E M I C O N D U C T I V E

C E R A M I C C A P A C I T O R

P

T A N T A L U M

C A P A C I T O R

T U B U L A R

S

C A P A C I T O R

C E R A M I C

F I L M

S U L F I D E

P O L Y P H E N Y L E N E

C A P A C I T O R

R E S I S T O R

R E M A R K S

N O M A R K

P A R T S

N A M E

C A R B O N

C A R B O N

M E T A L

M E T A L

M E T A L

F I R E

C E M E N T

S E M I

F I L M

R E S I S T O R

F I L M

R E S I S T O R

O X I D E

F I L M

R E S I S T O R

F I L M

R E S I S T O R

P L A T E

R E S I S T O R

P R O O F C A R B O N

F I L M

R E S I S T O R

M O L D E D

R E S I S T O R

V A R I A B L E

R E S I S T O R

( P = 5 )

( P = 1 0 )

C H I P

R E S I S T O R

N O T I C E

U . S . A

G

C A N A D A

E U R O P E

L

C H I N A

A U S T R A L I A

S I N G A P O R E

K O R E A

G E N E R A L

U

C

T

A

K

R

J A P A N

( m o d e l )

B

B R I T I S H

J

S O U T H E U R O P E

E

V

T A I W A N

F

R U S S I A N

P

L A T I N A M E R I C A

S

B R A Z I L

H

T H A I

Timer (16-bit)

Internal peripheral functions

Inputs (timer B): 6

Three-phase motor control circuit

Outputs (timer A): 5

Watchdog timer

(15-bit)

Remote control signal

receiver

(2 circuits)

PWM function (8-bit x 2)

CEC function

Real-time clock

VCC1 ports

VCC2 ports

A/D converter

(10-bit resolution X 26 channels)

System clock generator

PLL frequency synthesizer

On-chip oscillator (125 kHz)

High-speewd on-chip oscillator

X

IN

-X

OUT

X

CIN

-X

COUT

Port P0

8

Port P1

8

Port P2

8

Port P3

8

Port P4

8

Port P5

8

Port P12

8

Port P13

8

Port P14

2

Port P11

8

Port P10

8

Port P9

8

Port P8

8

Port P7

8

Port P6

8

ISP

USP

INTB

SB

CRC arithmetic circuit

(CRC-CCITT or CRC-16)

DMAC (4 channels)

Voltage detecter

On-chip debugger

Power-on reset

Multiplier

Memory

ROM

RAM

FB

A1

FLG

PC

UART or

clock synchronous serial I/O

Clock synchronous serial I/O

Multi-master I

2

C-bus interface

(6 channels)

(8 bit x 2 channels)

(1 channel)

D/A converter

(8-bit resolution X 2 circuits)

M16C/60 series

Microprocessor core

R0L

R0H

R1H

R1L

R2

R3

FB

A1

A0

IC22

: R1EX25032ATA00A

Serial peripheral interface 32 k EEPROM (4-kword × 8-bit)

Vcc

8

Vss

4

S

1

W

3

C

6

Serial-parallel converter

Y-select and Sense amp.

Memory array

High voltage generator

HOLD

7

D

5

Q

2

Control logic

Address generator

Y

decoder

X

decoder

IC21

: R5F3651TNFC

Single chip 16-bit microprocessor

V

DD

CE

Vref

4

3

1

2

Current Limit

V

OUT

GND

Pin No.

1

2

3

4

Symbol

V

OUT

GND

CE

V

DD

Description

Output Pin

Ground Pin

Chip Enable ("H" Active)

Input Pin

IC24, 25

: RP130Q331D-TR-F

Voltage regulator

IC27

: SN74LVC1G17DCKR

Single schmitt-trigger buffer

1

2

3

5

4

NC

A

GND

VCC

Y

INPUT

A

OUTPUT

Y

L

H

L

H

IC26

:

TC7WH126FK

Dual bus buffer

1

G1

2

A1

3

Y2

4

GND

8 Vcc

7 G2

6 Y1

5 A2

EEPROM

No replacement part available.

to DIGITAL 1/5

to DIGITAL 3/5

to DIGITAL 4/5

to DIGITAL 5/5

to DIGITAL 3/5, 4/5

Writing port

L101

L201

RX-V475/HTR-4066

RX-V500D

no_use

BKP1005HS680-T

no_use

BKP1005HS680-T

to DIGITAL 4/5

to AM/FM TUNER

(for factory)

(RX-V475/HTR-4066)

RX-V475/HTR-4066

RX-V500D

Summary of Contents for RX-V500D

Page 9: ...RX V500D A model RX V500D B G models 9 RX V475 HTR 4066 RX V500D RX V475 HTR 4066 RX V500D ...

Page 132: ... CONFIGURING THE SYSTEM SETTINGS RX V475 HTR 4066 RX V500D 133 ...

Page 133: ... システム設定を変更する RX V475 HTR 4066 RX V500D 134 ...

Page 146: ...147 RX V475 HTR 4066 RX V500D RX V475 HTR 4066 RX V500D MEMO ...

Page 147: ...RX V475 HTR 4066 RX V500D ...