CIRCUIT DESCRIPTION

The block diagram and following circuit descrip

tion will provide you with a better underst anding

of the design of this transceiver. The circuit

description is tailored to the full-feature FT-

1 0 1 ZD, and the reader should note that the

counter unit and digital display are optional

features for the FT- 1 0 1 Z.

The FT- 1 0 1 ZD consists of a premix-type single

conversion sy stem, using a 9 MHz IF for all m odes

o f operation.

RECEIVER

The RF input signal from the antenna is fed

through antenna relay RL2 , lamp fuse FH2 ,

attenuator swit ch S2oo4 (lo cated on the LEVER

SW unit , PB- 1 97 5 ) , 9 MHz trap L2 1 o 1 and C 1 20 7

(located on the TRIMMER A UNIT) , and input

t ransformer T 1 to pin 3 of the RF UNIT .

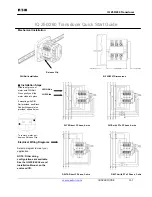

RF

UNIT (PB- 1 96 0)

The incoming signal is amplified by the RF

amplifier, Q 1 0 1

( 3 SK5 1 -03 ) ,

a dual-gate M OSFET

used in a grounded source configuration . This

transistor has superior immunity from intermodula

tion distortion. The amplified signal is then fed

through a source follower, Q 1 02

(J3 1 0 ) ,

to the

balanced mixer consisting o f Q 1 o 3 and Q l o4

(2SK1 9GR ) ,

where the input signal is heterodyned

with the local oscillator signal . The lo cal signal is

delivered from buffer amplifier Q 1 07

( 2N44 27 ) ,

and the resulting IF signal of 8 . 9 8 7 5 MHz is fed

through T 1 0 2 to J 1 0 1 .

The input and output of the RF amplifier are

permeability-tuned circuits, resulting in high sensi

tivity and excellent rej e ction of unwanted out-of

band signals.

'

1

- -

-

-

- - -

-

-

-R

:-

R

;-

A

:;

- -

-

-

R

;;

F

�

M-;:- - -R:-M-:- - -

- - - - - - - - -

00 1

002

003

T i

I

3SK51 · 03

J310

2SK19GR

ROS

1 00

T2 I

I

I

i�

I

I

I

I

I

1 2 V

�_!'���-R��N_!!��l____l_

_ _ - - - - - - - - _ - - - -

-

- - - - - _ _ _

J

-

2 2

-