Manual VIPA CPU 21x

Chapter 1

Principles

HB103E - Rev. 05/45

1-5

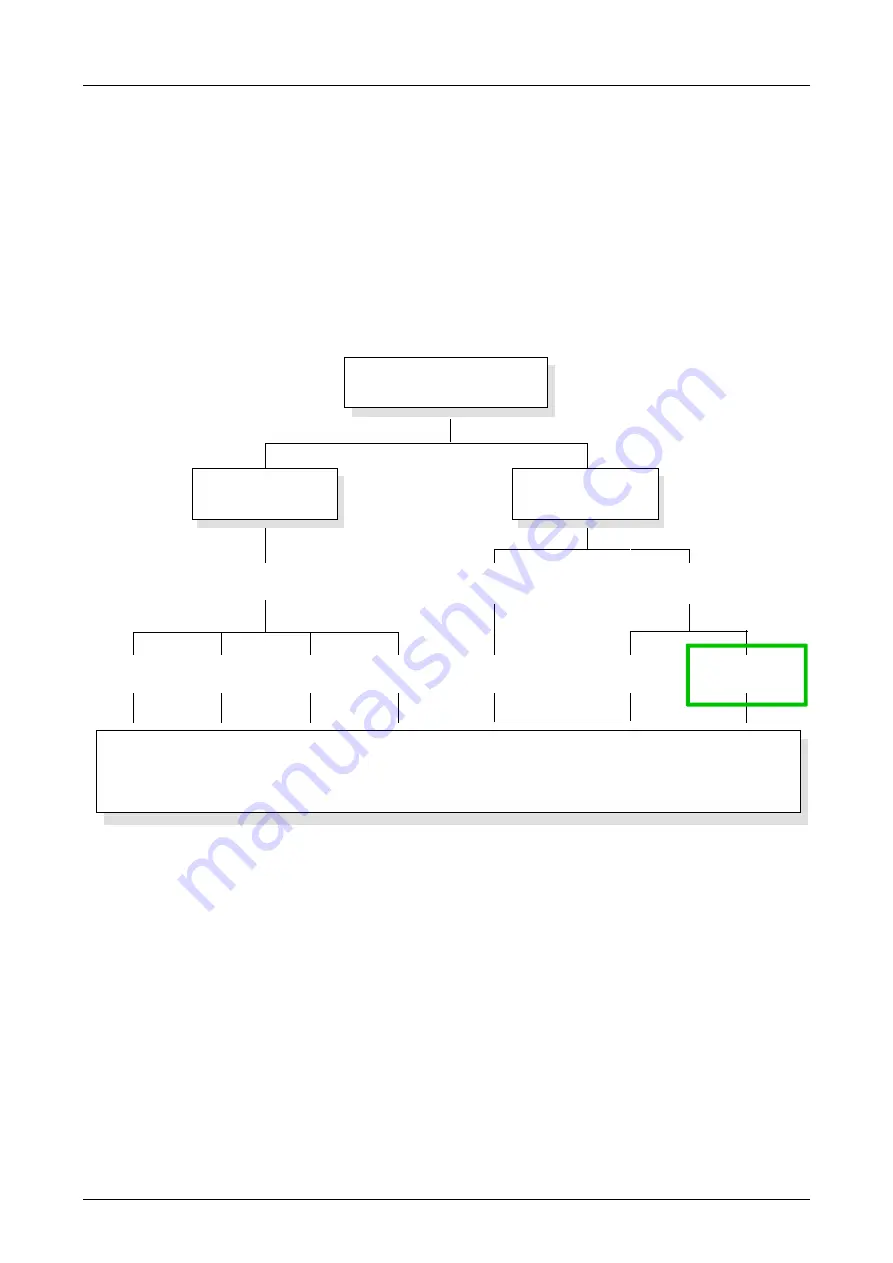

Overview System 200V

The System 200V is a modular automation system for low and middle

range of performance that you may use either centralized or decentralized.

The single modules are directly clipped to a 35mm DIN rail and are

connected together with the help of special bus clips.

The following picture shows the range of performance of the System 200V:

System 200V

decentral

peripheral

Profibus DeviceNet CAN Interbus PC-CPU PLC-CPU PLC-CPU

Dig. IN / Dig. OUT / Anal. IN / Anal. OUT / FM / CP

DP 200V

PC 200V

PLC 200V

for STEP

®

5 of Siemens

for STEP

®

7 of Siemens

central

The current manual describes the PLC-CPU family CPU 21x compatible to

STEP

7 by Siemens.

The description of the PLC-CPU-family CPU 24x compatible to STEP

5 by

Siemens is available in the manual No. HB99.

The peripheral modules, PCs and decentralized peripheral equipment are

to find in the manual HB97 "System 200V". This manual also contains hints

for installation and commissioning of the System 200V.

The System 200V

Overview

Manuals

Summary of Contents for CPU 21 Series

Page 1: ...Manual VIPA CPU 21x Order No VIPA HB103E Rev 05 45 ...

Page 2: ...Lerrzeichen ...

Page 6: ...About this Manual Manual VIPA CPU 21x Subject to change to cater for technical progress ...

Page 10: ...Contents Manual VIPA CPU 21x iv HB103E Rev 05 45 ...

Page 30: ...Chapter 1 Principles Manual VIPA CPU 21x 1 18 HB103E Rev 05 45 ...

Page 58: ...Chapter 2 Hardware description Manual VIPA CPU 21x 2 28 HB103E Rev 05 45 ...

Page 80: ...Chapter 3 Deployment CPU 21x Manual VIPA CPU 21x 3 22 HB103E Rev 05 45 ...

Page 178: ...Chapter 5 Deployment CPU 21x 2BT02 with H1 TCP IP Manual VIPA CPU 21x 5 48 HB103E Rev 05 45 ...