July 17, 2002

114

PCB Layout Guidelines

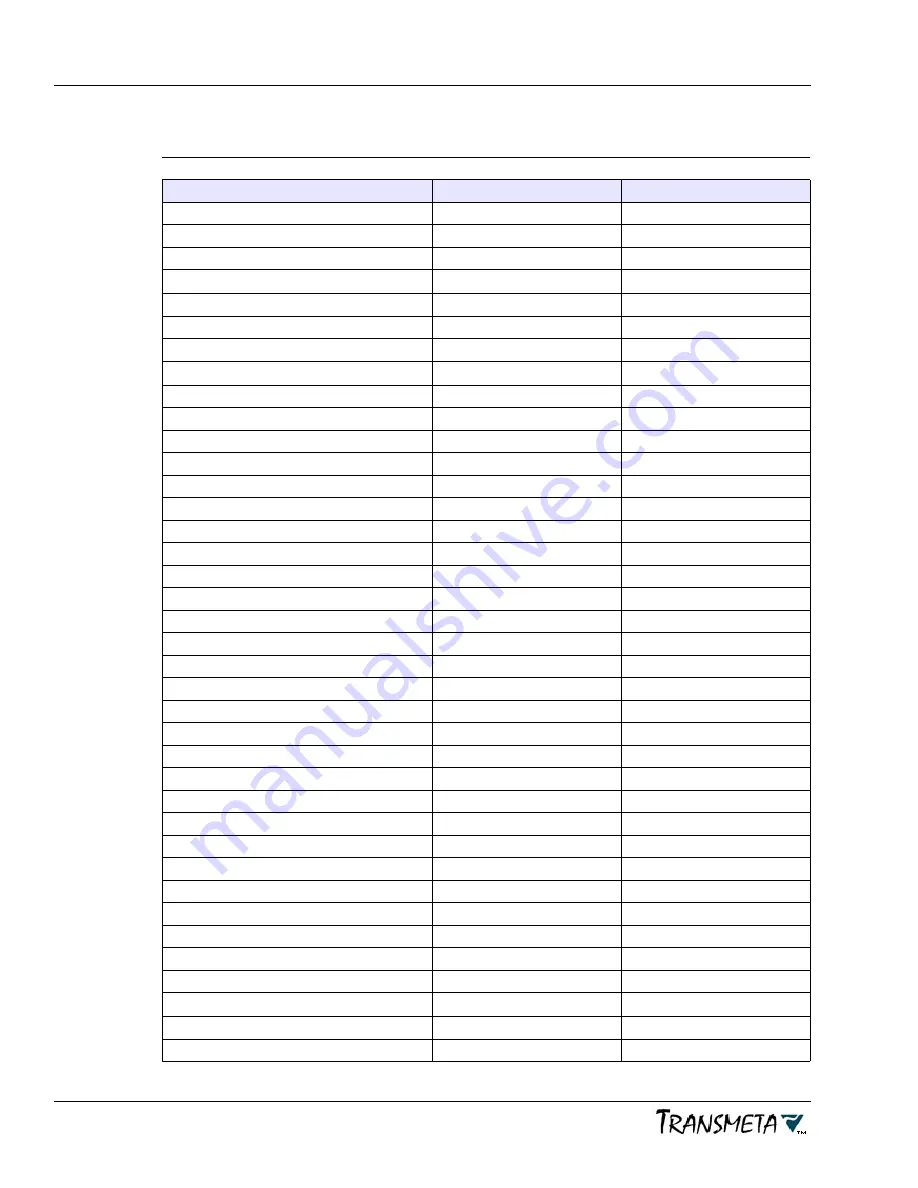

7.3.3 Allegro Extended Spacing Constraints

Table 19:

Extended Global Spacing/Line/Via Constraints

1

Constraint Name

Default Constraint Value

BGA Constraint Value

Pin-to-pin

5 mils

5 mils

Line-to-pin

5 mils

5 mils

Line-to-line

5 mils

5 mils

Via-to-pin

Note

2

Note

2

Via-to-via

10 mils

10 mils

Via-to-line

5 mils

5 mils

Shape-to-pin

5 mils

5 mils

Shape-to-via

5 mils

Note

2

Shape-to-line

5 mils

5 mils

Shape-to-shape

5 mils

5 mils

Thru pin-to-thru pin

5 mils

5 mils

Thru pin-to-SMD pin

5 mils

5 mils

Thru pin-to-test pin

5 mils

5 mils

Thru pin-to-thru via

10 mils

6 mils

Thru pin-to-test via

10 mils

6 mils

Thru pin-to-buried blind via

10 mils

6 mils

Thru pin-to-line

5 mils

5 mils

Thru pin-to-shape

5 mils

5 mils

SMD pin-to-SMD pin

5 mils

5 mils

SMD pin-to-test pin

5 mils

5 mils

SMD pin-to-thru via

8 mils

7 mils

SMD pin-to-test

8 mils

7 mils

SMD pin-to-buried blind via

8 mils

7 mils

SMD pin-to-line

5 mils

5 mils

SMD pin-to-shape

5 mils

5 mils

Test pin-to-test pin

5 mils

5 mils

Test pin-to-thru via

10 mils

6 mils

Test pin-to-test via

10 mils

6 mils

Test pin-to-buried blind via

10 mils

6 mils

Test pin-to-line

5 mils

5 mils

Test pin-to-shape

5 mils

5 mils

Thru via-to-thru via

10 mils

10 mils

Thru via-to-test via

10 mils

10 mils

Thru via-to-buried blind via

10 mils

10 mils

Thru via-to-line

5 mils

5 mils

Thru via-to-shape

5 mils

Note

2

Test via-to-test via

10 mils

10 mils

Test via-to-buried blind via

10 mils

10 mils

Summary of Contents for Crusoe TM5500

Page 1: ...TM5500 TM5800 System Design Guide July 17 2002...

Page 6: ...July 17 2002 6 List of Tables...

Page 8: ...July 17 2002 8 List of Figures...

Page 50: ...July 17 2002 50 Processor Power Supplies and Power Management...

Page 110: ...July 17 2002 110 System Design Considerations...

Page 122: ...July 17 2002 122 System Design Checklists...

Page 128: ...July 17 2002 128 Serial Write protection PLD Data...

Page 130: ...July 17 2002 130 Index...