DPWM 0-3 Registers Reference

73

SNIU028A – February 2016 – Revised April 2016

Copyright © 2016, Texas Instruments Incorporated

Digital Pulse Width Modulator (DPWM)

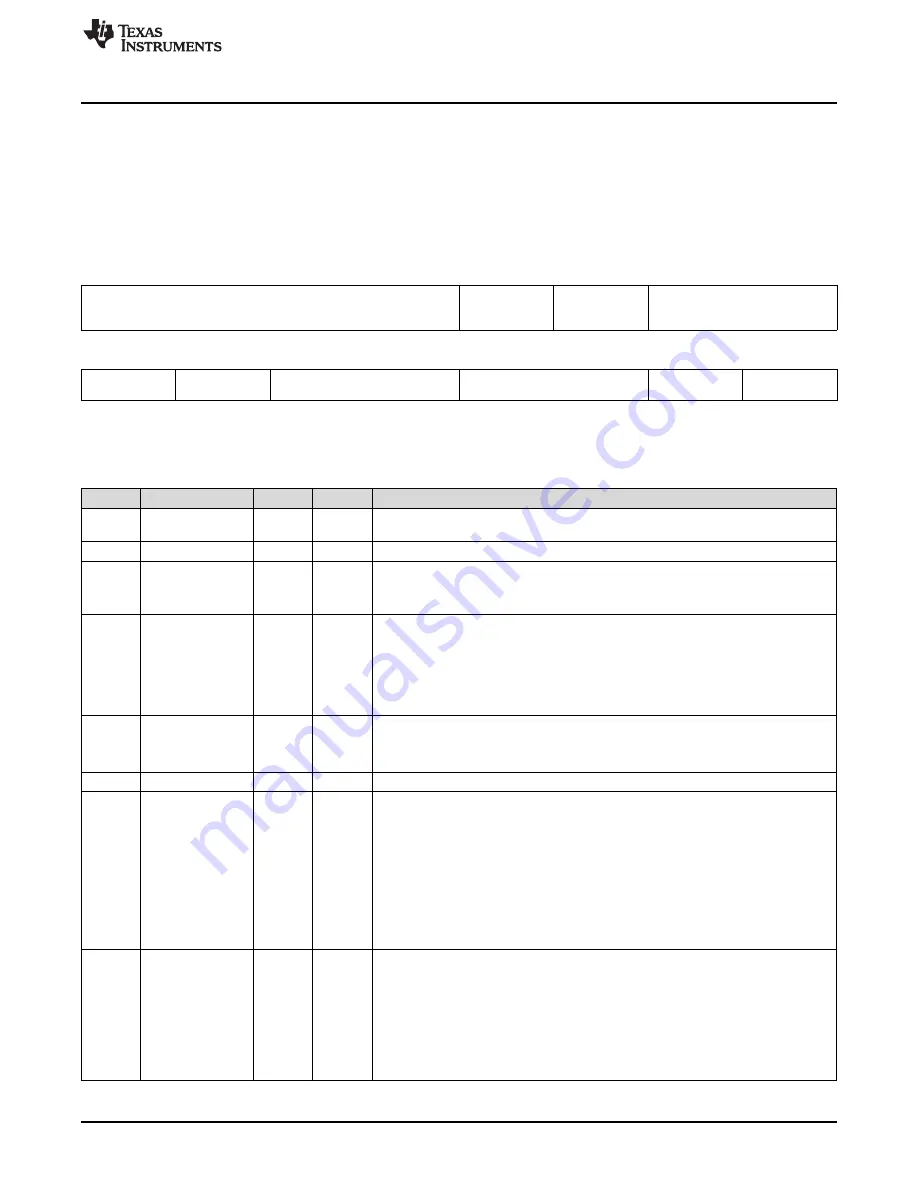

2.31.3 DPWM Control Register 2 (DPWMCTRL2)

Address 00050008 – DPWM 3 Control Register 2

Address 00070008 – DPWM 2 Control Register 2

Address 000A0008 – DPWM 1 Control Register 2

Address 000D0008 – DPWM 0 Control Register 2

Figure 2-19. DPWM Control Register 2 (DPWMCTRL2)

15

14

13

12

11

10

9

8

SYNC_IN_DIV_RATIO

Reserved

RESON_DEAD

TIME_COMP

_EN

FILTER_DUTY_SEL

R/W-0000

R-0

R/W-0

R/W-00

7

6

5

4

3

2

1

0

IDE_DUTY_B

_EN

Reserved

SAMPLE_TRIG1

_OVERSAMPLE

SAMPLE_TRIG1_MODE

SAMPLE_TRIG

_2_EN

SAMPLE_TRIG

_1_EN

R/W-0

R-0

R/W-00

R/W-00

R/W-0

R/W-1

LEGEND: R/W = Read/Write; R = Read only; -

n

= value after reset

Table 2-8. DPWM Control Register 2 (DPWMCTRL2) Register Field Descriptions

Bit

Field

Type

Reset

Description

15-12

SYNC_IN_DIV

_RATIO

R/W

0000

Sets the number of syncs to be masked before a resync

11

Reserved

R

0

10

RESON_DEAD

TIME_COMP_EN

R/W

0

Sets the method at which High Side CLA-Duty is used in calculations 0 = CLA Duty

from Filter (Default)

1 = CLA Duty from Filter minus deadtime adjustment

9-8

FILTER_DUTY

_SEL

R/W

00

Sets which register is sent to the Resonant Duty input of the Filter. Settings of 0 and

1 enable the 16 bit signed value of the Resonant Duty register to be added to the

Filter Period value for period adjustment in resonant mode.

0 = PWM Period Register (Default)

1 = Event 2

2 = DPWM Resonant Duty Register (Bits 13:0)

7

IDE_DUTY_B_EN

R/W

0

IDE Duty Cycle Side B Enable

0 = Disabled (Default)

1 = Enabled

6

Reserved

R

0

5-4

SAMPLE_TRIG1

_OVERSAMPLE

R/W

00

Oversample Select for Sample Trigger 1

00 = Trigger an EADC Sample at PWM Sample Trig Register value (Default)

01 = Trigger an EADC Sample at PWM Sample Trig Register value and at PWM

Sample Trig Register value divided by 2

10 = Trigger a EADC Sample at PWM Sample Trig Register value, at PWM Sample

Trig Register value divided by 2 and at PWM Sample Trig Register value divided by

4

11 = Trigger a EADC Sample at PWM Sample Trig Register value, at PWM Sample

Trig Register value divided by 2, at PWM Sample Trig Register value divided by 4

and at PWM Sample Trig Register value divided by 8

3-2

SAMPLE_TRIG1

_MODE

R/W

00

Mode select for Sample Trigger 1

00 = Trigger value is set using PWM Sample Trig Register value (Default)

01 = Trigger value is adaptive midpoint (EV1+CLA_DUTY/2 + Adaptive Offset) and

uses current CLA value at update event

10 = Trigger value is adaptive midpoint (EV1+CLA_DUTY/2 + Adaptive Offset) and

uses previous CLA value at update event

11 = Trigger value is adaptive midpoint (EV1+CL Fixed Adaptive

Offset) and uses current CLA value at update event