SLOU186F

–

AUGUST 2006

–

REVISED AUGUST 2010

4

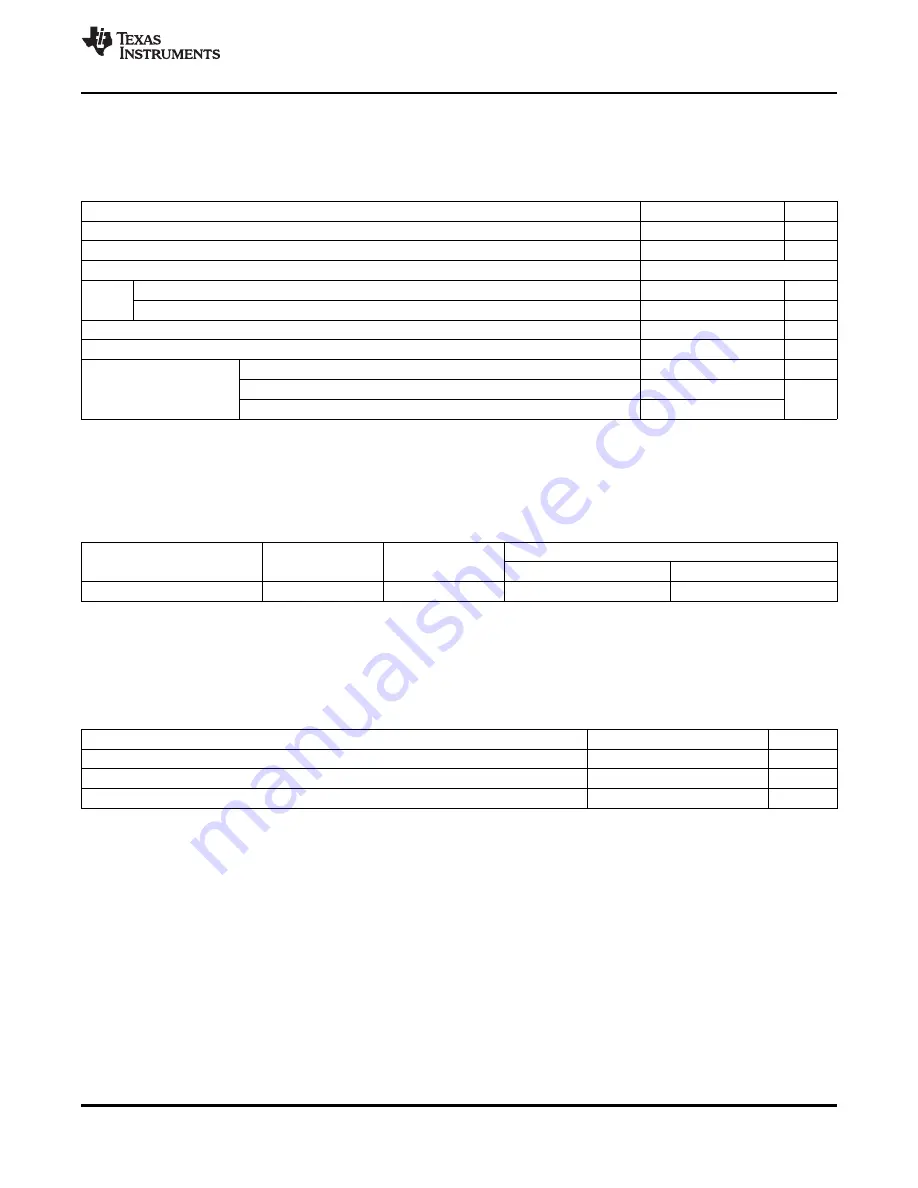

ELECTRICAL SPECIFICATIONS

4.1

ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)

(1)

VALUE

UNIT

VIN

Supply voltage

6

V

I

O

Output current

150

mA

Continuous power dissipation

See Dissipation Ratings Table

Maximum junction temperature, any condition

(2)

140

°

C

T

J

Maximum junction temperature, continuous operation, long-term reliability

(2)

125

°

C

T

stg

Storage temperature range

–

55 to 150

°

C

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds

300

°

C

HBM (human body model)

2

kV

ESDS rating

CDM (charged device model)

500

V

MM (machine model)

200

(1)

The absolute maximum ratings under any condition is limited by the constraints of the silicon process. Stresses above these ratings may

cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are

stress ratings only and functional operation of the device at these or any other conditions beyond those specified are not implied.

(2)

The maximum junction temperature for continuous operation is limited by package constraints. Operation above this temperature may

result in reduced reliability and/or lifetime of the device.

4.2

DISSIPATION RATINGS TABLE

POWER RATING

(2)

θ

JC

θ

JA

(1)

PACKAGE

(

°

C/W)

(

°

C/W)

T

A

≤

25

°

C

T

A

= 85

°

C

RHB (32)

31

36.4

2.7 W

1.1 W

(1)

This data was taken using the JEDEC standard high-K test PCB.

(2)

Power rating is determined with a junction temperature of 125

°

C. This is the point where distortion starts to increase substantially.

Thermal management of the final PCB should strive to keep the junction temperature at or below 125

°

C for best performance and

long-term reliability.

4.3

RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

MIN

TYP

MAX

UNIT

VIN

Supply voltage

2.7

5

5.5

V

T

J

Operating virtual junction temperature range

–

40

125

°

C

T

A

Operating ambient temperature range

–

40

25

110

°

C

Copyright

©

2006

–

2010, Texas Instruments Incorporated

ELECTRICAL SPECIFICATIONS

7

focus.ti.com: