2 Quick Start

2.1 Input Power

2.1.1 Input Power (Labeled VPWR)

The DC input voltage is provided through J1 on the motherboard (screw jack). A DC power supply or wall

adapter with sufficient current capacity can power the EVM.

CAUTION

Reverse voltage protection is not provided; ensure that the correct polarity is applied to J1.

This DC input is labeled

VPWR

in the schematics, is used for port VBUS and for the TPS23882B1 devices. The

VPWR connections to the PoE ports are not fused. Each two-pair port is capable of furnishing at least 30 W.

The minimum PSE port voltage is 44 VDC for type 1 and 50 V for type 2 and type 3. During evaluation, choose

the appropriate DC power supply for different environments.

2.1.2 Local 3.3 V (Labeled 3.3 V)

Local 3.3 V for local devices (labeled as 3.3 V) is provided by the onboard LM5019 buck converter. The LM5019

provides a basic power-on sequence and provides a well-controlled and consistent start-up. In addition to 54 V,

the TPS23882B1 requires 3.3 V for the digital circuitry and this is routed up to TPS23882B1EVM-008 over the

connector interface. The current consumption is 6-mA typical and 12-mA maximum.

2.1.3 External 3.3 V (Labeled 3.3 V_USB)

The BOOST-PSEMTHR8-097 provides galvanic isolation between the PoE power side and host side using

digital isolators (ISO7241CD). The host side power is provided either from J2 of the mother board (from

) or J5 of the motherboard (from

CAUTION

Do not use USB2ANY and LaunchPad simultaneously.

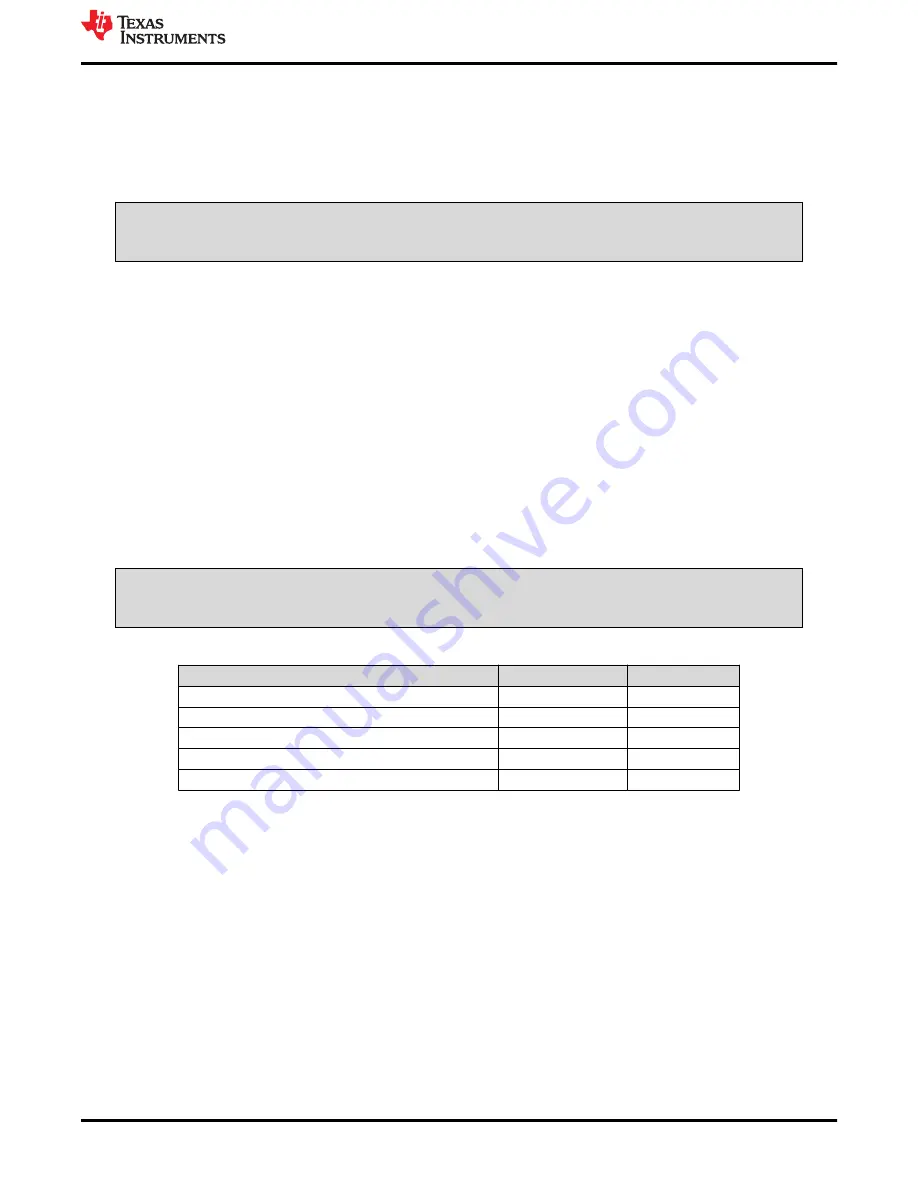

Table 2-1. TPS23882B1 Voltage Rail Current Requirements

Voltage Rail

Typical (mA)

Maximum (mA)

3.3 V_USB

2.5

3

3.3 V

6

12

VPWR (Miscellaneous)

35

57

VPWR (8 × 2 Pair Ports)

4800

5455

VPWR Total (8 × 2 Pair Ports)

4835

5512

2.2 PoE Port Interfaces

The TPS23882B1 device must be configured through the host to become operational if the device is

not configured to autonomous mode(described in section 2.4). This EVM provides 2 ways to control the

TPS23882B1: TPS238x EVM GUI (with

) and Basic Reference Code (with

LaunchPad).

2.2.1 IEEE802.3bt 2-Pair Ports

Eight 2-pair ports are provided at J19, J20, J8, J7, J32, J33, J21, and J9 of the motherboard for 2-pair ports 1, 2,

3, 4, 5, 6, 7, and 8 respectively. The power furnished is according to alternative A with MDI-X polarity.

2.3 I

2

C Interfaces

Two I

2

C interfaces to the TPS23882B1 are provided on the EVM.

2.3.1 USB2ANY

J2 of the motherboard provides an interface with the

adapter when using a PC and GUI.

Quick Start

SLVUC36 – APRIL 2021

TPS23882B1EVM: PoE, PSE, TPS23882B1

Evaluation Module

3

Copyright © 2021 Texas Instruments Incorporated