Clocking and Framing Data

2-7

McBSP Operation

SPRU592E

2.3 Clocking and Framing Data

This section explains basic concepts and terminology important for

understanding how McBSP data transfers are timed and delimited.

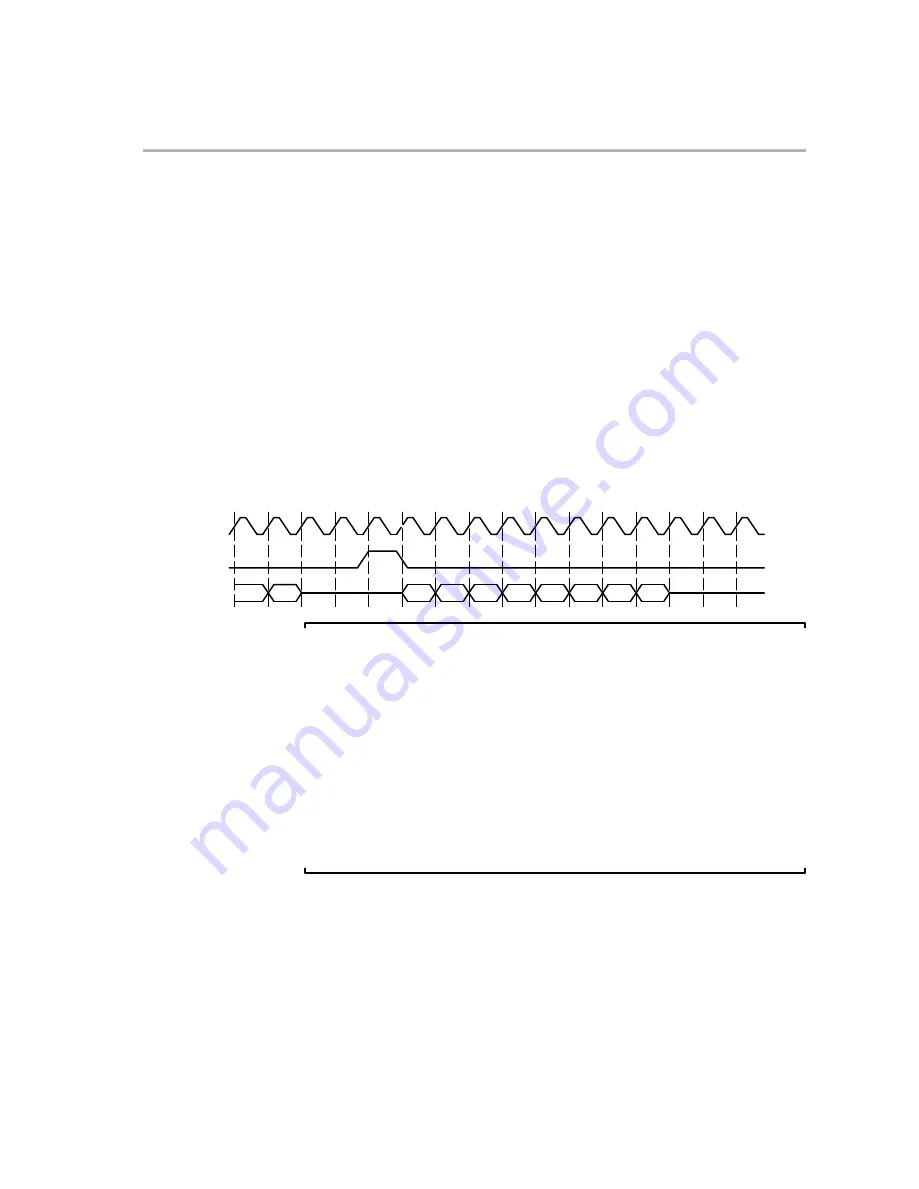

2.3.1 Clocking

Data is shifted one bit at a time from the DR pin to the RSR(s) or from the

XSR(s) to the DX pin. The time for each bit transfer is controlled by the rising

or falling edge of a clock signal.

The receive clock signal (CLKR) controls bit transfers from the DR pin to the

RSR(s). The transmit clock signal (CLKX) controls bit transfers from the

XSR(s) to the DX pin. CLKR or CLKX can be derived from a pin at the boundary

of the McBSP or derived from inside the McBSP. The polarities of CLKR and

CLKX are programmable.

In the following example, the clock signal controls the timing of each bit transfer

on the pin.

D(R/X)

FS(R/X)

CLK(R/X)

B0

B1

B2

B3

B4

B5

B6

B7

A0

A1

ÁÁ

ÁÁ

Á

Á

ÁÁ

ÁÁ

Internal

Internal

Note:

The maximum frequency for the McBSP on the TMS320VC5503/5507/5509

and TMS320VC5510 devices is 1/2 the CPU clock frequency. The maximum

frequency for the McBSP on the TMS320VC5501 and TMS320VC5502

devices is 1/2 the frequency of the slow peripherals clock. For more

information on programming the frequency of the slow peripheral clock, see

the device-specific data manual for detailed information on the McBSP

timing requirements.

When driving CLKX or CLKR at the pin, choose an appropriate input clock

frequency. When using the internal sample rate generator for CLKX and/or

CLKR, choose an appropriate input clock frequency and divide down value

(CLKGDV).

2.3.2 Serial Words

Bits traveling between a shift register (RSR or XSR) and a data pin (DR or DX)

are transferred in a group called a

serial word

. You define how many bits are

in a word.

Bits coming in on the DR pin are held in RSR until RSR holds a full serial word.

Only then is the word passed to RBR (and ultimately to the DRR).

Summary of Contents for TMS320VC5509

Page 5: ...vi This page is intentionally left blank ...

Page 43: ...McBSP Operation 2 20 SPRU592E This page is intentionally left blank ...

Page 105: ...SPI Operation Using the Clock Stop Mode 6 16 SPRU592E This page is intentionally left blank ...

Page 187: ...Transmitter Configuration 8 40 SPRU592E This page is intentionally left blank ...

Page 191: ...General Purpose I O on the McBSP Pins 9 4 SPRU592E This page is intentionally left blank ...

Page 201: ...Emulation Power and Reset Considerations 10 10 SPRU592E ...

Page 207: ...Data Packing Examples 11 6 SPRU592E This page is intentionally left blank ...

Page 273: ...McBSP Register Worksheet 13 14 SPRU592E This page is intentionally left blank ...