CPU Registers

2-6

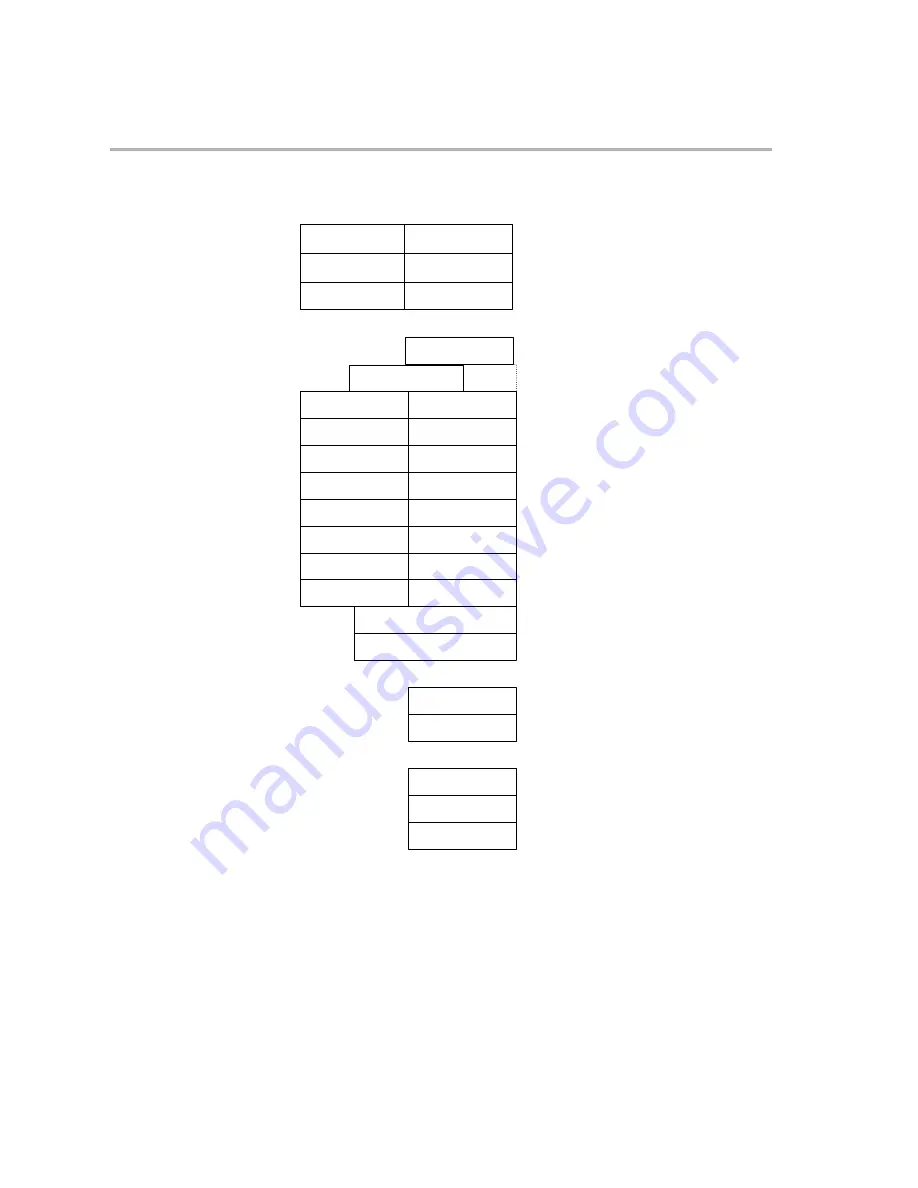

Figure 2

−

2. C28x Registers

6/7-bit

offset

†

SP[16]

DP[16]

AR0[16]

AR1[16]

AR2[16]

AR3[16]

AR4[16]

AR5[16]

AR6[16]

AR7[16]

AR0H[16]

AR1H[16]

AR2H[16]

AR3H[16]

AR4H[16]

AR5H[16]

AR6H[16]

AR7H[16]

XAR0[32]

XAR1[32]

XAR2[32]

XAR3[32]

XAR4[32]

XAR5[32]

XAR6[32]

XAR7[32]

PC[22]

RPC[22]

ST0[16]

IER[16]

ST1[16]

DBGIER[16]

IFR[16]

T[16]

PH[16]

TL[16]

PL[16]

AL[16]

AH[16]

XT[32]

P[32]

ACC[32]

†

A 6-bit offset is used when operating in C28x mode or C27x object-compatible mode.

A 7-bit offset is used when operating in C2xLP source-compatible mode. The least significant

bit of the DP is ignored when operating in this mode.

2.2.1 Accumulator (ACC, AH, AL)

The accumulator (ACC) is the main working register for the device. It is the

destination for all ALU operations except those which operate directly on

memory or registers. ACC supports single-cycle move, add, subtract, and

Summary of Contents for TMS320C28x

Page 30: ...1 12...

Page 80: ...This page intentionally left blank 2 50 This page intentionally left blank...

Page 269: ...IN loc16 PA 6 112 MOV AL 0 AL 0 UOUT IORegC AL IOspace IORegC AL 10...

Page 308: ...MAXCUL P loc32 6 151 Saturate MOVL Var64 2 ACC Store result into Var64 MOVL Var64 P...

Page 509: ...SUBL ACC P PM 6 352 SUBL ACC P PM ACC S B 11 M X 4 MOVH Y ACC 5 Store Q15 result into Y...

Page 585: ...This page intentionally left blank 7 32 This page intentionally left blank...