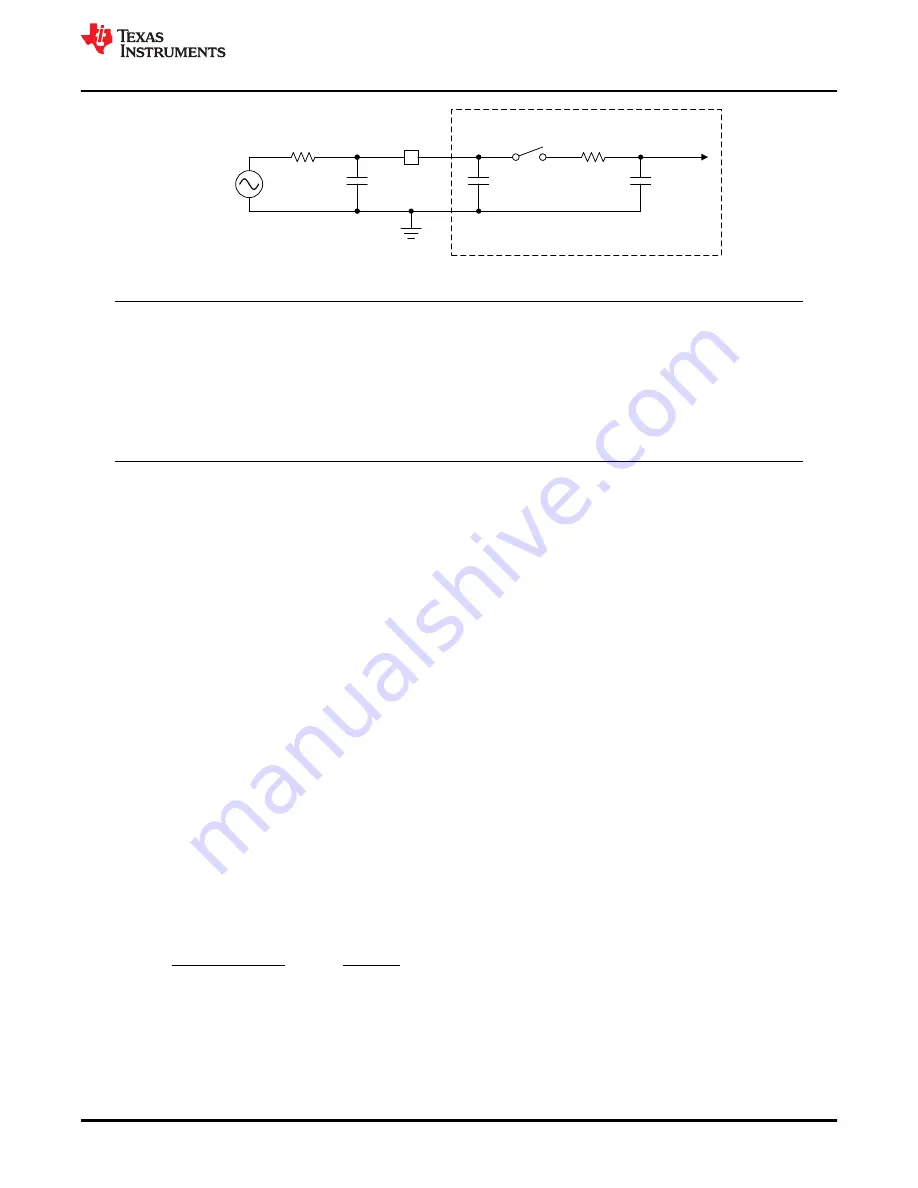

Internal to device

To ADC

ADCINx

R

s

Source

Signal

C

s

C

p

5pF

S+H

Switch

C

h

1.6pF

R

on

3.4k

Figure 8-3. ADCINx Input Model

Note

The ADC does not precondition the Ch capacitor voltage before conversions, therefore the following

behaviors apply:

1. There is no predetermined ADC conversion value when the ADCIN pin is not connected to a

Source Signal.

2. Residual charge will remain on Ch between ADC conversions.

3. Sequential conversions may suffer from cross-talk if the ACQPS window is too short for Ch to

settle.

For correct operation, the input signal to the ADC must be allowed adequate time to charge the sample and hold

capacitor, C

h

. Typically, the S+H duration is chosen such that C

h

will be charged to within ½ LSB or ¼ LSB of the

final value, depending on the tolerable settling error.

The S+H time required to satisfy the settling error is largely influenced by the bandwidth of the source

signal. Therefore, the following recommendations for approximating the S+H duration will be simplified into

two practical scenarios of either high bandwidth or low bandwidth signals. A high bandwidth source signal will

be characterized as being able to meet the settling error and real-time requirements of the system using a

supported ACQPS setting. A low bandwidth source signal is one that requires a longer S+H duration than is

acceptable.

8.2.1.1 ACQPS Approximation for High Bandwidth Signals

Signals that must be sampled frequently with minimal phase delay (such as feedback sensors used in control-

loop calculations) are high bandwidth signals. These signal paths require a small R

s

C

s

time constant as seen by

the ADCINx pin. An external signal buffer (such as an op-amp) may be used to boost the sampling bandwidth;

such buffers should ideally have a bandwidth that is high enough to fully charge C

h

within the selected ACPQS

S+H window.

8.2.1.1.1 ACQPS Approximation Equations for High Bandwidth Signals

An approximation of the required settling time can be determined using an RC settling model. The time constant

(τ) for the model is given by the equation:

ì

=

:

4

O

+

4

KJ

;:

%

D

;

+

:

4

O

;

k

%

O

+

%

L

o

And the number of time constants needed is given by the equation:

G

= ln

l

2

J

OAPPHEJC

ANNKN

p F

ln

l

%

O

+

%

L

%

D

p

So the total S+H time (t

S+H

)should be set to at least:

P

O

+

D

=

G

®

ì

Analog-to-Digital Converter (ADC)

SPRUH18I – JANUARY 2011 – REVISED JUNE 2022

TMS320x2806x Microcontrollers

515

Copyright © 2022 Texas Instruments Incorporated

Summary of Contents for TMS320 2806 Series

Page 2: ......