Board Layout

28

SNVU472B – October 2016 – Revised August 2018

Copyright © 2016–2018, Texas Instruments Incorporated

The LP8756xQ1EVM (SV601325) Evaluation Module

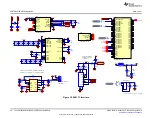

This layer is similar to mid-layer2 to reduce resistance of the VIN net.

Figure 26. Mid-Layer3

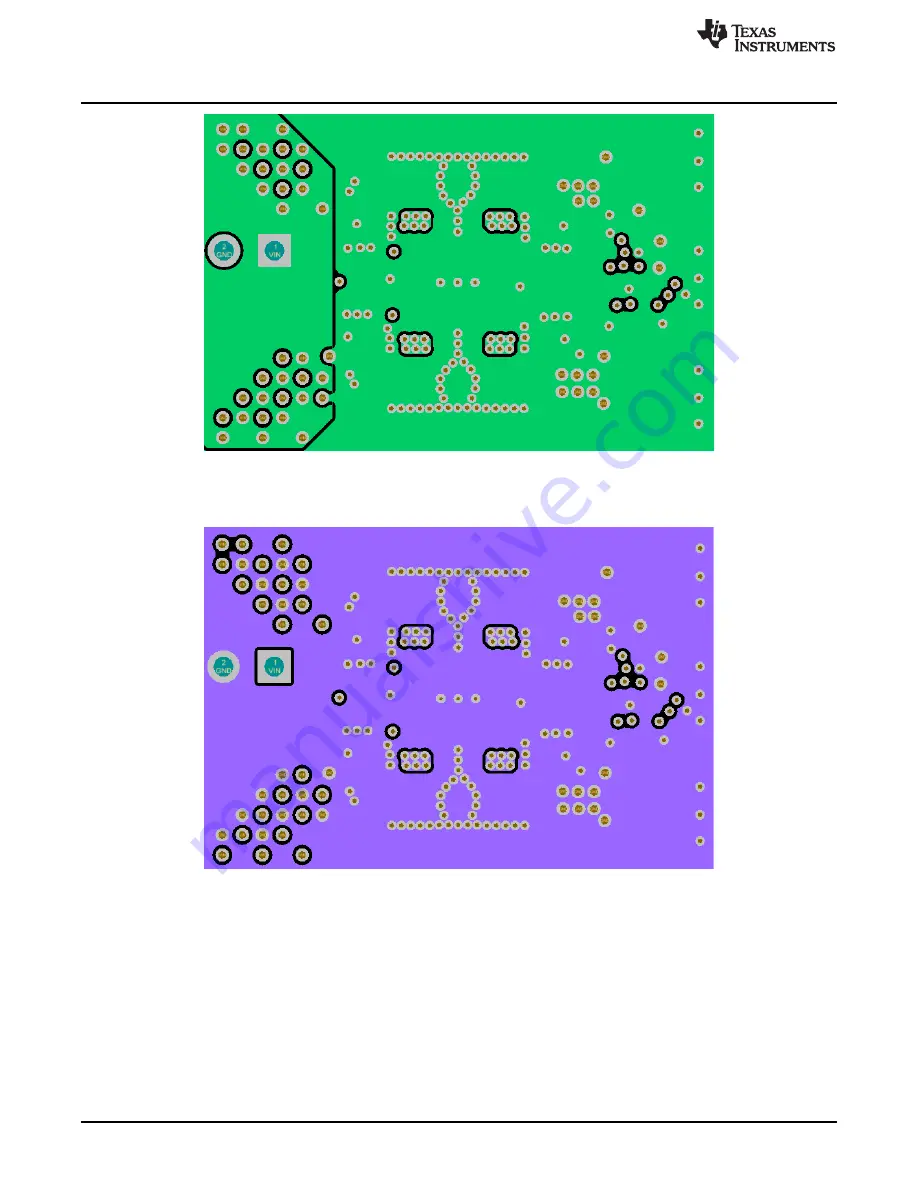

Placed close to bottom layer (0.063 mm) to reduce parasitic inductance.

Figure 27. Mid-Layer4, GND Plane