I

2

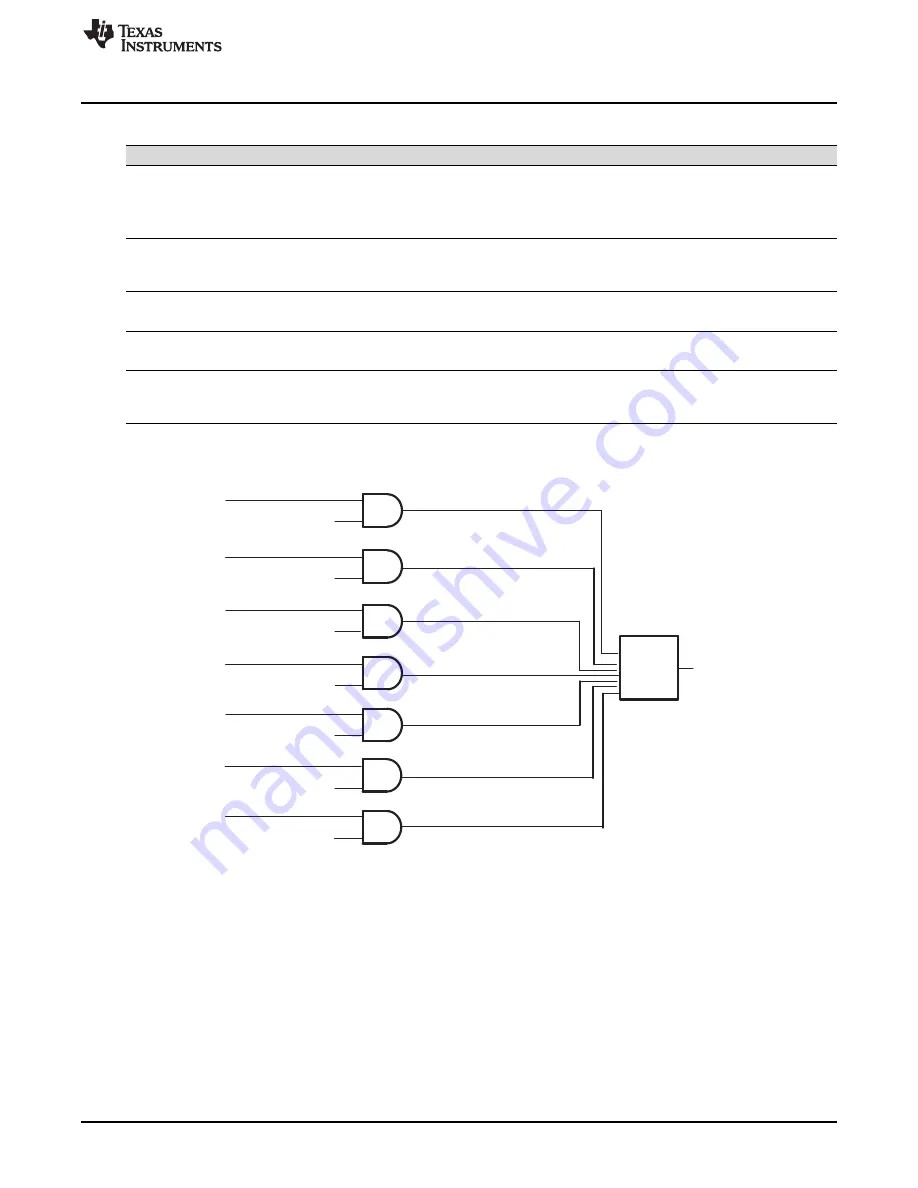

C interrupt

request to CPU

I2CIER(XRDY)

I2CSTR(XRDY)

XRDYINT

I2CIER(RRDY)

I2CIER(ARDY)

I2CSTR(RRDY)

I2CSTR(ARDY)

RRDYINT

ARDYINT

I2CIER(AL)

I2CSTR(AL)

I2CSTR(NACK)

I2CIER(NACK)

ALINT

NACKINT

Flag bits

Enable bits

I

2

C interrupt requests

Arbiter

I2CIER(AAS)

I2CIER(SCD)

AASINT

SCDINT

I2CSTR(SCD)

I2CSTR(AAS)

Interrupt Requests Generated by the I2C Module

1055

SPRUHE8E – October 2012 – Revised November 2019

Copyright © 2012–2019, Texas Instruments Incorporated

C28 Inter-Integrated Circuit Module

Table 14-3. Descriptions of the Basic I2C Interrupt Requests (continued)

I2C Interrupt Request

Interrupt Source

ARDYINT

Register-access ready condition: The I2C module registers are ready to be accessed because the

previously programmed address, data, and command values have been used.

The specific events that generate ARDYINT are the same events that set the ARDY bit of I2CSTR.

As an alternative to using ARDYINT, the CPU can poll the ARDY bit.

NACKINT

No-acknowledgment condition: The I2C module is configured as a master-transmitter and did not

received acknowledgment from the slave-receiver.

As an alternative to using NACKINT, the CPU can poll the NACK bit of I2CSTR.

ALINT

Arbitration-lost condition: The I2C module has lost an arbitration contest with another master-transmitter.

As an alternative to using ALINT, the CPU can poll the AL bit of I2CSTR.

SCDINT

Stop condition detected: A STOP condition was detected on the I2C bus.

As an alternative to using SCDINT, the CPU can poll the SCD bit of the status register, I2CSTR.

AASINT

Addressed as slave condition: The I2C has been addressed as a slave device by another master on the

I2C bus.

As an alternative to using AASINT, the CPU can poll the AAS bit of the status register, I2CSTR.

Figure 14-13. Enable Paths of the I2C Interrupt Requests

14.3.2 I2C FIFO Interrupts

In addition to the seven basic I2C interrupts, the transmit and receive FIFOs each contain the ability to

generate an interrupt (I2CINT2A). The transmit FIFO can be configured to generate an interrupt after

transmitting a defined number of bytes, up to 16 . The receive FIFO can be configured to generate an

interrupt after receiving a defined number of bytes, up to 16. These two interrupt sources are ORed

together into a single maskable CPU interrupt. The interrupt service routine can then read the FIFO

interrupt status flags to determine from which source the interrupt came. See the I2C transmit FIFO

register (I2CFFTX) and the I2C receive FIFO register (I2CFFRX) descriptions.

14.4 Resetting/Disabling the I2C Module

You can reset/disable the I2C module in two ways:

•

Write 0 to the I2C reset bit (IRS) in the I2C mode register (I2CMDR). All status bits (in I2CSTR) are