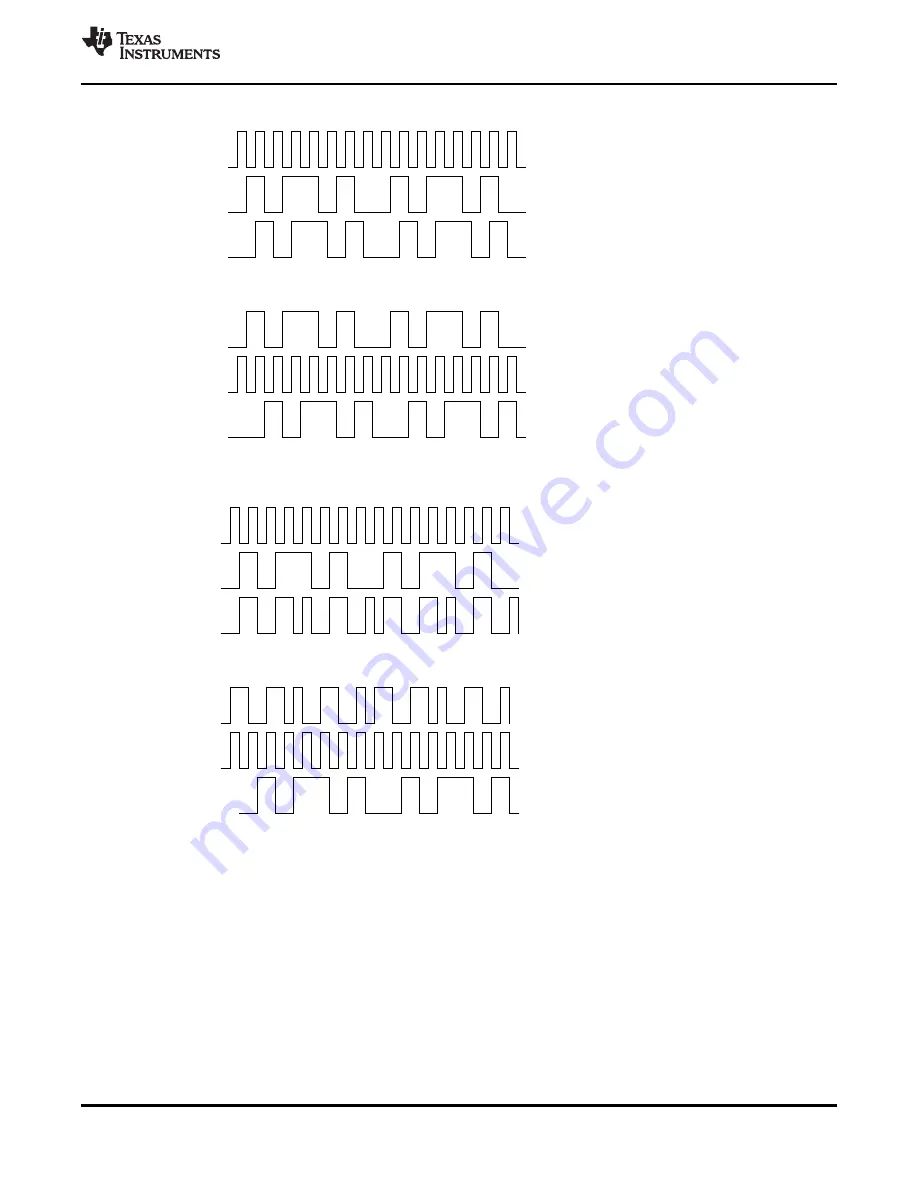

Clock provided by CC1020

FSK modulating signal (Manchester

encoded), internal in CC1020

Data provided by microcontroller

Transmitter side:

Clock provided by CC1020

Demodulated signal (Manchester

encoded), internal in CC1020

Data provided by CC1020

DCLK

DIO

“RF”

“RF”

DCLK

DIO

Receiver side:

Clock provided by CC1020

FSK modulating signal (Manchester

encoded), internal in CC1020

Data provided by microcontroller

Transmitter side:

Clock provided by CC1020

Demodulated signal (Manchester

encoded), internal in CC1020

Data provided by CC1020

DCLK

DIO

“RF”

“RF”

DCLK

DIO

Receiver side:

Clock provided by CC1020

FSK modulating signal (NRZ),

internal in CC1020

Data provided by microcontroller

Transmitter side:

Clock provided by CC1020

Demodulated signal (NRZ),

internal in CC1020

Data provided by CC1020

DCLK

DIO

“RF”

“RF”

DCLK

DIO

Receiver side:

Clock provided by CC1020

FSK modulating signal (NRZ),

internal in CC1020

Data provided by microcontroller

Transmitter side:

Clock provided by CC1020

Demodulated signal (NRZ),

internal in CC1020

Data provided by CC1020

DCLK

DIO

“RF”

“RF”

DCLK

DIO

Receiver side:

SWRS046H – NOVEMBER 2006 – REVISED MARCH 2015

Figure 5-6. Synchronous NRZ Mode (SEP_DI_DO = 0)

Figure 5-7. Synchronous Manchester Encoded Mode (SEP_DI_DO = 0)

Copyright © 2006–2015, Texas Instruments Incorporated

Detailed Description

23

Product Folder Links: