A E3 Design Changes

The AM243x LaunchPad had various design changes for the E3 revision of the board. The changes are listed

below:

1.

RJ45 Connector Component Replaced

Table A-1. E3 RJ45 Connector

AM243x LP E2

AM243x LP E3

74991116144A from Wurth Electronics

LPJG16314A4NL from Link-PP with common center tap

2.

eFUSE Programming Voltage LDO Driven by a Header Rather than GPIO

a. The E2 revision of the AM243x Launchpad used GPIO0_53 to enable the VPP regulator for eFUSE

Programming. In the E3 revision, the enable line is connected to pin 2 of a two pin header (J22.2).

Connecting a jumper across the two pins will enable the LDO.

b. A resistor was added in the E3 revision to pull-up pin one (J22.1) of the VPP enable header to

VSYS_3V3.

3.

GPIO Mapping Changes

a. The E3 revision made various changes to the GPIO mapping, below is a table describing the changes.

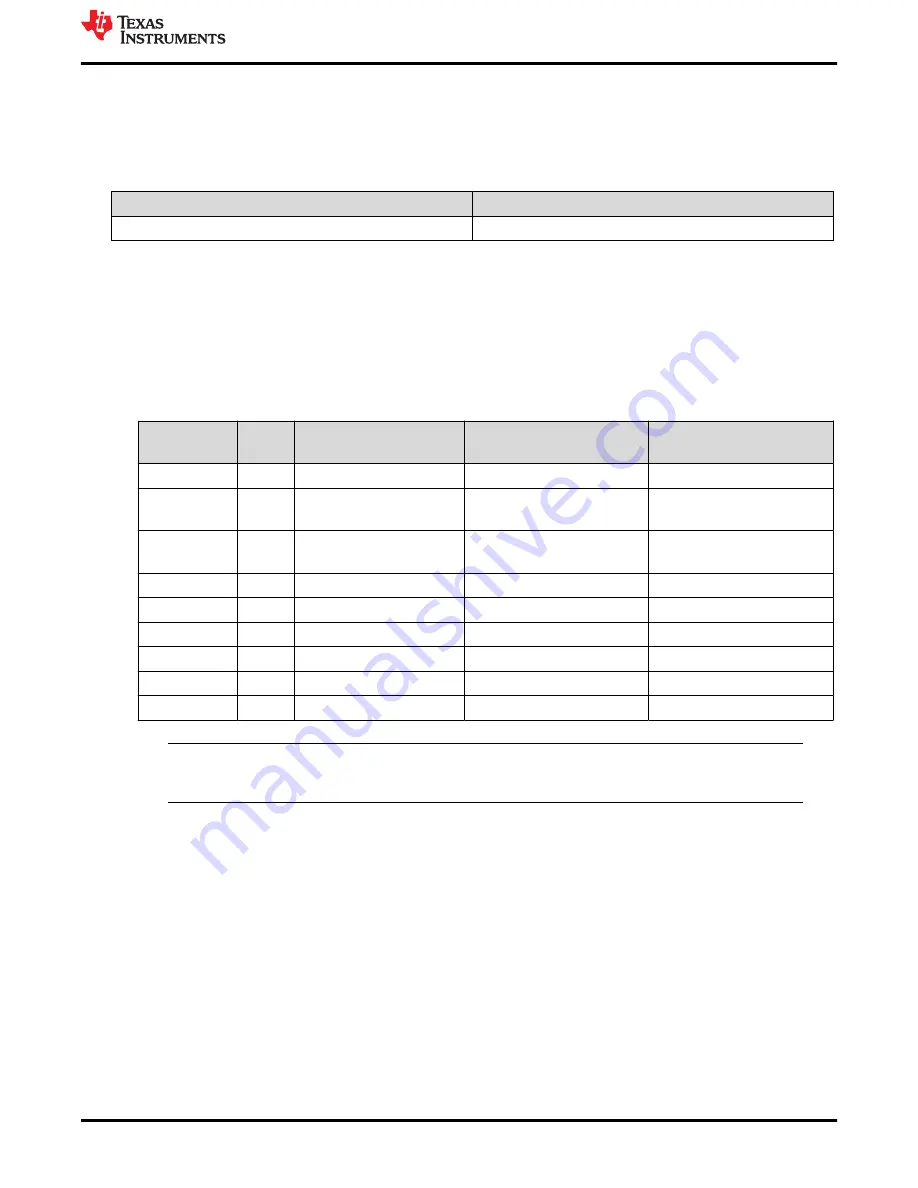

Table A-2. E3 GPIO Mapping

Package Signal

Name

GPIO

Number

E2 Net Name

E3 Net Name

Description

GPMC_AD13

GPIO0_28

FSI/BP_MUX_SEL

GPIO_RGMII1_PHY_RSTn

To reset the RGMII1 Ethernet PHY

GPMC_AD12

GPIO0_27

USER_LED2

PRG_CPSW_RGMII1_MUX_SEL

To select the RGMII1 path between PRG

and CPSW

GPMC0_AD11

GPIO0_26

USER_LED1

FSI/BP_MUX_SEL

To select the functionality of GPMC0_AD8

and GPMC0_AD9 pins as FSI_RX or PWM

PRG1_PRU1_GPO5

GPIO0_70

PRG_CPSW_RGMII1_MUX_SEL

PRG1_CPSW_ETH2_LED_1000/RX_ER

Ethernet PHY2 RX ER indication to SoC

PRG1_PRU1_GPO8

GPIO0_73

GPIO_RGMII1_PHY_RSTn

PRG1_CPSW_ETH2_LED_LINK

Ethernet PHY2 RX link indication to SoC

PRG1_PRU0_GPO5

GPIO0_50

GPIO0_50

PRG1_CPSW_ETH1_LED_1000/RX_ER

Ethernet PHY1 RX ER indication to SoC

PRG1_PRU0_GPO8

GPIO0_53

VPP_1V8_REG_EN

PRG1_CPSW_ETH1_LED_LINK

Ethernet PHY1 RX link indication to SoC

PRG1_PRU0_GPO9

GPIO0_54

CPSW_RGMII1_TX_CTL

PRG1_CPSW_ETH1_LED_ACT

Ethernet PHY1 MII COL indication to SoC

PRG1_PRU1_GPO9

GPIO0_74

CPSW_RGMII1_TD1

PRG1_CPSW_ETH2_LED_ACT

Ethernet PHY2 MII COL indication to SoC

Note

GPIO Mapping for signals not present in this table have the same mapping for E2 and E3

revisions of the LaunchPad

4.

Bootmode Isolation Buffer Component Change

a. The E2 Revision of the AM243x LaunchPad only supported input signals for balls connected to the

Bootmode isolation buffer (U32) since the DIR pin was connected to ground. In E3 the Bootmode

isolation buffer is changed from SN74AVC8T245PWR to TXB0106PWR. Because the E3 isolation buffer

is bi-directional, input and output signals are supported.

b. The TXB0106PWR OE enable pin places all outputs in a high impedence state when OE = low. The

inverter gate was removed in the E3 Revision because the OE pin can be connected directly to PORz.

c. The BOOTMODE0/2/10 signals connected to the buffer had the respective pull-up or pull-down resistor

updated from 10kΩ to 49.9kΩ

5.

Ethernet PHY Connections

a. The following Ethernet PHY signals were not connected to the AM243x GPIO in the E2 Revision:

• PRG1_CPSW_ETH1_LED_LINK

• PRG1_CPSW_ETH2_LED_LINK

• PRG1_CPSW_ETH1_LED_1000/RX_ER

• PRG1_CPSW_ETH2_LED_1000/RX_ER

• PRG1_CPSW_ETH1_LED_ACT

E3 Design Changes

SPRUJ12B – AUGUST 2021 – REVISED OCTOBER 2022

AM243x LaunchPad™ Development Kit User's Guide

81

Copyright © 2022 Texas Instruments Incorporated