Model DMM7510 7½ Digit Multimeter Application Manual

Section 5: Grading and binning resistors

DMM7510-904-01 Rev. D March 2021

5-3

If a resistor passes the 20% limit test, the resistance value is checked against limit 2, which is the

10% limit value. If the resistor fails this limit inspection, the resistance is outside of the 10% tolerance

band. The trigger model outputs the limit 2 fail pattern, which causes the component handler to place

the resistor in the limit 2 fail bin (10% fail bin).

If a resistor passes the 10% limit test, the resistance value is checked against limit 3, which is the 5%

limit value, and so on. If a resistor passes all the limit tests, the trigger model outputs the overall pass

bit pattern, which causes the component handler to place the resistor in the all pass bin.

For this example, the same fail pattern is assigned to both the lower and upper bounds of the limits.

Therefore, a fail bin contains resistance values in the range (Resistance

− Percentage to

Resi Percentage). The percentage is 20, 10, 5, or 1. You can assign different bit patterns for

different limit values.

Trigger-model template: GradeBinning

The GradeBinning trigger-model template contains the settings for the number of components, digital

I/O, and limits. The command parameters for the template are described in the following commands

and table.

SCPI command usage:

:TRIGger:LOAD "GradeBinning", <components>, <startInLine>, <startDelay>, <endDelay>,

<limit1High>, <limit1Low>, <limit1Pattern>, <allPattern>, <limit2High>,

<limit2Low>, <limit2Pattern>, <limit3High>, <limit3Low>, <limit3Pattern>,

<limit4High>, <limit4Low>, <limit4Pattern>, "<bufferName>"

TSP command usage:

trigger.model.load("GradeBinning",

components

,

startInLine

,

startDelay

,

endDelay,

limit1High

,

limit1Low

,

limit1Pattern

,

allPattern

,

limit2High

,

limit2Low

,

limit2Pattern

,

limit3High

,

limit3Low

,

limit3Pattern

,

limit4High

,

limit4Low

,

limit4Pattern

,

bufferName

)

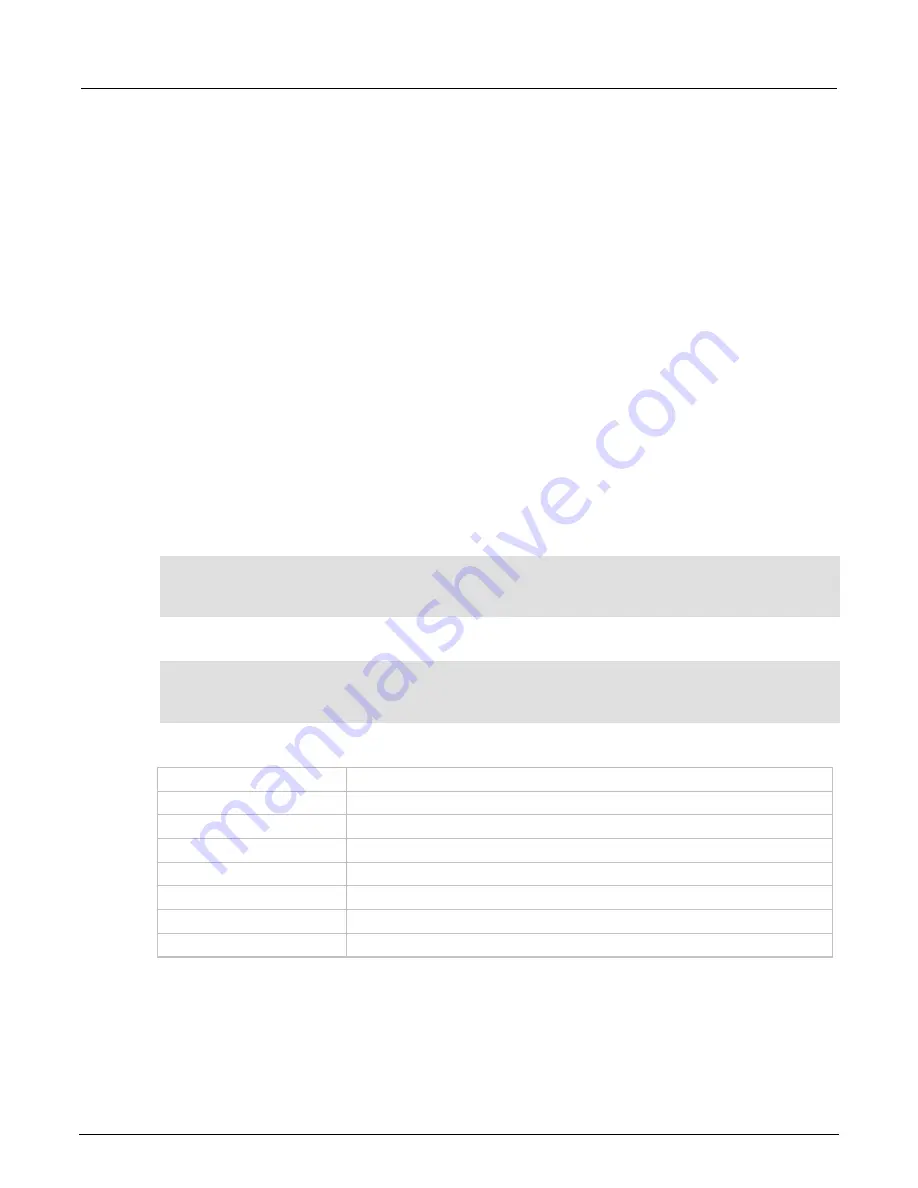

Parameter list

components

100

startInLine

Digital I/O line 5

startDelay

100 ms

endDelay

100 ms

limit1High

Resistance = 100

Ω, Percentage = 20%, 100 + 20% = 120 Ω

limit1Low

Resistance = 100

Ω, Percentage = 20%, 100

−

20% = 80

Ω

limit1Pattern

Bin 1 fail pattern 15: Drive all digital I/O lines high (1111)

allPattern

All pass pattern 4: Drive line 3 high (0100)