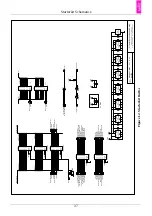

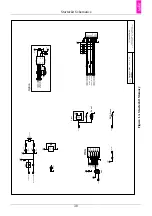

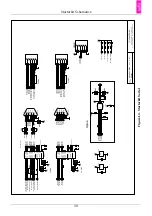

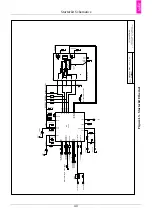

Starterkit Schematics

38

A-09

/

6

3

14.07.2011

mk

MEMORY

Funktion:

Seite:

Projekt:

Tel. +49 (0)30 611295-0 Fax. +49 (0)30 611295-10

Datum:

Autor:

LP-Nr.:

Revision:

StampG45-Base

19.101.01

(C) taskit GmbH

Groß-Berliner Damm 37, D-12487 Berlin

JTAG

Option

DNP

BMS, Erase

Option

DNP

DNP

Reset

8

DAT1

7

DAT0

6

VSS

5

CLK

4

VDD

3

CMD

2

CD/DAT3

1

DAT2

11

CASE

12

CASE

X5

MICROSD

C55

100nF

R39

68k

R40

68k

R41

6k8

R42

68k

R43

68k

R96

100r

R97

100r

R98

100r

R99

100r

R100

100r

R101

100r

3

VCC

1

GND

2

-RES

IC10

MAX803

1

2

J2

1

TCK

2

GND

3

TDO

4

VTREF

5

TMS

6

-SRST

7

VSUP

8

-TRST

9

TDI

10

GND

X12

Wanne 10 pol

C104

100nF

SP1

PS1240P02CT3

TDK

e

13

12

11

IC18-D

74LVC86

R24

330r

e

9

10

8

IC18-C

74LVC86

R25

330r

14

VCC

7

GND

IC18-E

74LVC86

C80

100nF

1

2

J10

8

SO

1

SI

2

SCK

4

-CS

3

-RES

6

VCC

7

GND

5

-WP

IC11

AT45UNI

J11

R10

100r

J14

C9

100nF

J18

J19

R13

10k

e

4

5

6

IC18-B

74LVC86

J8

J7

1

2

J48

J49

R17

100k

SW2

DTSM61N

PA3/MCI0_DA1/TCKL4

PA2/MCI0_DA0/TIOB3

PA0/MCI0_CK/TCLK3

PA1/MCI0_CDA/TIOA3

PA5/MCI0_DA3/TIOB4

PA4/MCI0_DA2/TIOA4

+3V3

+3V3

NRST

TCK

TDO

TMS

TDI

NTRST

NRST

+3V3

+3V3

RTCK

+3V3

+3V3

+3V3

BMS

PB0/SPI0_MISO

PB1/SPI0_MOSI

PB2/SPI0_SPCK

PB3/SPI0_NPCS0

NRST

+3V3

-AT45CS

+3V3

+3V3

PE26/LCDD19

PD8/AC97FS/TIOB5

+3V3

JTAGSEL

+3V3

Figure

I.3.

Starterkit

Memory