UM2

4

69

Ele

c

tric

al

sch

emat

ics

UM2

469

Re

v 1

43

/59

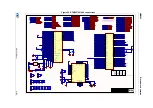

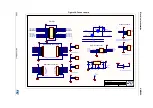

Figure 27. PSRAM

5

12

PSRAM

MB1260

D02

11/09/2018

Title:

Size:

Reference:

Date:

Sheet:

of

A4

Revision:

STM32F723E/F7308 DISCOVERY

Project:

LCD_PSRAM_D[0..15]

PSRAM_A[0..17]

PSRAM

3V3

3V3

3V3

Place close to PSRAM

PSRAM_NE1

LCD_PSRAM_D0

LCD_PSRAM_D1

LCD_PSRAM_D2

LCD_PSRAM_D3

LCD_PSRAM_D4

LCD_PSRAM_D5

LCD_PSRAM_D6

LCD_PSRAM_D7

LCD_PSRAM_D8

LCD_PSRAM_D9

LCD_PSRAM_D10

LCD_PSRAM_D11

LCD_PSRAM_D12

LCD_PSRAM_D13

LCD_PSRAM_D14

LCD_PSRAM_D15

PSRAM_A0

PSRAM_A1

PSRAM_A2

PSRAM_A3

PSRAM_A4

PSRAM_A5

PSRAM_A6

PSRAM_A7

PSRAM_A8

PSRAM_A9

PSRAM_A10

PSRAM_A11

PSRAM_A12

PSRAM_A13

PSRAM_A14

PSRAM_A15

PSRAM_A16

PSRAM_A17

PSRAM_A[0..17]

LCD_PSRAM_D[0..15]

LCD_PSRAM_NWE

LCD_PSRAM_NOE

PSRAM_NE1

PSRAM_NBL0

PSRAM_NBL1

PSRAM_NBL0

PSRAM_NBL1

LCD_PSRAM_NOE

LCD_PSRAM_NWE

i

PSRAM_A

Matched Net Lengths [Tolerance = 200mil]

Impedance Constraint [Min = 40.00 Max = 60.00 ]

i

PSRAM_D

Matched Net Lengths [Tolerance = 200mil]

Impedance Constraint [Min = 40.00 Max = 60.00 ]

i

PSRAM_A

i

PSRAM_A i

PSRAM_A

i

PSRAM_A

10K

R63

0

R65

0

R64

PSRAM Data, NWE & NOE

shared with LCD

100nF

C63

100nF

C71

A4

B4

A3

B3

A2

A5

A1

A4

A0

A3

CS1

B5

I/O0

B6

I/O1

C5

I/O2

C6

I/O3

D5

VDD

D6

GND

D1

I/O4

E5

I/O5

F5

I/O6

F6

I/O7

G6

WE

G5

A16

E4

A15

F4

A14

F3

A13

G4

A12

G3

A11

H5

A10

H4

A9

H3

A8

H2

I/O8

B1

I/O9

C1

I/O10

C2

I/O11

D2

VDD

E1

I/O12

E2

I/O13

F2

I/O14

F1

I/O15

G1

LB

A1

UB

B2

OE

A2

A7

D4

A6

C4

A5

C3

A17

D3

A18

H1

GND

E6

NC

G2

CS2

A6

NC

H6

NC

E3

U10

IS66WV51216EBLL-55BLI

i

PSRAM_A

10K

R100