Copyright

c

2016, SiFive Inc. All rights reserved.

13

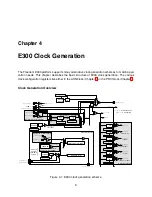

When

pllsel

is clear, the

hfroscclk

directly drives

hfclk

. The

pllsel

bit is clear on wakeup

reset.

The

pllcfg

register is reset to: bypass and power off the PLL

pllbypass

=1; input driven from

external HFXOSC oscillator

pllrefsel

=1; PLL not driving system clock

pllsel

=0; and the PLL

ratios are set to R=2, F=64, and Q=8 (

pllr

=01,

pllf

=011111,

pllq

=11).

The PLL provides a lock signal which is set when the PLL has achieved lock, and which can be

read from the most-significant bit of the

pllcfg

register. The PLL requires up to 100

µ

s to regain

lock once enabled, and the lock signal will not necessarily be stable during this initial lock period

so should only be interrogated after this period. The PLL may not achieve lock and the lock signal

might not remain asserted if there is excessive jitter in the source clock.

The PLL requires dedicated 1.8 V power supply pads with a supply filter on the circuit board.

The supply filter should be a 100

Ω

resistor in series with the board 1.8 V supply decoupled with

a 100 nF capacitor across the VDDPLL/VSSPLL supply pins. The VSSPLL pin should not be

connected to board VSS.

PLL Output Divider

The

plloutdiv

register controls a clock divider that divides the output of the PLL.

0

31

9

plloutdivby1

8

0

7

6

plloutdiv

5

0

Figure 4.3: PLL Output Divider Register

plloutdiv

If the

plloutdivby1

bit is set, the PLL output clock is passed through undivided. If

plloutdivby1

is clear, the value

N

in

plloutdiv

sets the clock-divide ratio to 2

×

(

N

+ 1)

(between 2–128). The

output divider expands the PLL output frequency range to 0.375–384 MHz.

The

plloutdivby1

register is reset to divide-by-1 (

plloutdivby1

=1)..

Internal Low-Frequency Oscillator (LFRCOSC)

An untrimmed internal low-frequency RC oscillator can be provided with an operating frequency

of 40-80 kHz. The internal low-frequency oscillator can be used to clock the always-on domain in

lieu of an external crystal. A programmable prescalar is provided to allow runtime calibration of

the low-frequency output to improve timing accuracy.

External 32.768 kHz Low-Frequency Crystal Oscillator (LFXOSC)

A 32.768 kHz external crystal oscillator can be attached to provide a precise real-time clock. The

oscillator can be turned off to save power but can require up to 1 s to stabilize.

Summary of Contents for E300

Page 1: ...SiFive E300 Platform Reference Manual Version 1 0 1 c SiFive Inc ...

Page 2: ...2 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 4: ...ii SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 12: ...4 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 14: ...6 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 22: ...14 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 32: ...24 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 40: ...32 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 56: ...48 SiFive E300 Platform Reference Manual Version 1 0 1 ...

Page 60: ...52 SiFive E300 Platform Reference Manual Version 1 0 1 ...