CD-C471

VHiLA9241

M)

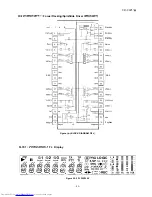

Pin No.

Port Name

Function

FIN2

Connection pin for photodiode of pickup.

RF signal is generated through addition with FIN pin, and FE signal is generated through subtraction.

2

Connection pin for photodiode of pickup.

3

Connection pin for ohotodiode of

TE

is aenerated throuah subtraction with

4

5

TB

6

7

TE

9

10

T H

11’

TA

Connection pin for photodiode of pickup.

Pin for input of DC component of TE signal.

Pin to connect gain setting resistor of TE signal to TE signal.

signal output pin.

TES (Track error sense) comparator input pin. TE signal is band-passed and input.

Input pin for shock detection.

Pin to set time constant of tracking gain.

amplifier output

12

13

T D

Pin to compose tracking phase compensation constant between TD and VR pins.

Pin to set tracking phase compensation.

14

JP

15

TO

16

FD

17

18

FA

19

Pin to set amplitude of tracking jump signal (kick pulse).

Tracking control signal output pin.

Focusing control signal output pin.

Pin to compose focusing phase compensation constant between FD and FA pins.

Pin to compose focusing phase compensation constant between

Pin to

phase

constant between FA and FE

20

FE

lo

pin of FE

21

22

AGND

23

24

25

SPG

26

Pin to connect gain setting resistor of FE signal across TE pin.

GND for analog signal.

Single end output for

and CV- pin input.

Spindle amplifier input.

Pin to connect aain settina resistor in the 12cm mode of

Pin to connect

phase

constant toaether with SPD

I

27

SPD

Spindle control

output pin.

SLEQ

Pin to connect thread phase compensation constant.

Thread control signal output pin.

Input pin of thread feed signal from micro computer.

input pin of thread feed signal from micro computer.

TGL

TOFF

36

TES

37

HFL

38

SLOF

39

40

41

RFSM

42

Input pin of tracking jump signal from DSP.

Input pin of tracking jump signal from DSP.

input pin of tracking gain control signal from DSP. TGL Gain low at

Input pin of

off control

from DSP. TOFF Off at

Output pin of TES signal to DSP.

(HIGH FREQUENCY LEVEL) is used to judge whether main beam is positioned on the bit or on the mirror.

Thread servo off control input pin.

Pin to input CLV error signal from DSP.

Pin to input CLV error signal from DSP.

RF output pin.

Pin to set aain of RF and set

constant toaether with RFSM

43

SLC

(SLICE LEVEL CONTROL) is the

to control of the level of the data slice with RF waveform DSP.

I

44

Input pin to control the level of data slice with DSP.

45

DGND

46

FSC

47

TBC

NC

49

DEF

GND pin in the digital system.

Output pin for focus search smoothening capacitor.

(Tracking Balance Control) Pin to set EF balance variable range.

Defect detection

of disk.

50

CLK

Reference clock input pin.

of DSP is input.

In this unit, the terminal with asterisk mark

is (open) terminal which is not connected to the outside.

46

Summary of Contents for CD-C471 W

Page 16: ... I I Ill I i c r __ __ I Figure 16 BLOCK DIAGRAM 2 3 16 ...

Page 17: ...CD C471 W w UTER lC56115621563 N5M4558L lC562 1 2 Figure 17 BLOCK DIAGRAM 3 3 17 ...

Page 36: ... POWER PWB B 1 MAII IUPWB P33 7 A 1 2 3 4 5 6 Figure 36 WIRING SIDE OF P W BOARD 6 8 36 ...

Page 54: ...CD C471 W MEMO 54 ...

Page 70: ......

Page 71: ...CD C471 W MEMO ...