IDT Configuration Registers

PES24T3G2 User Manual

8 - 46

February 22, 2012

Notes

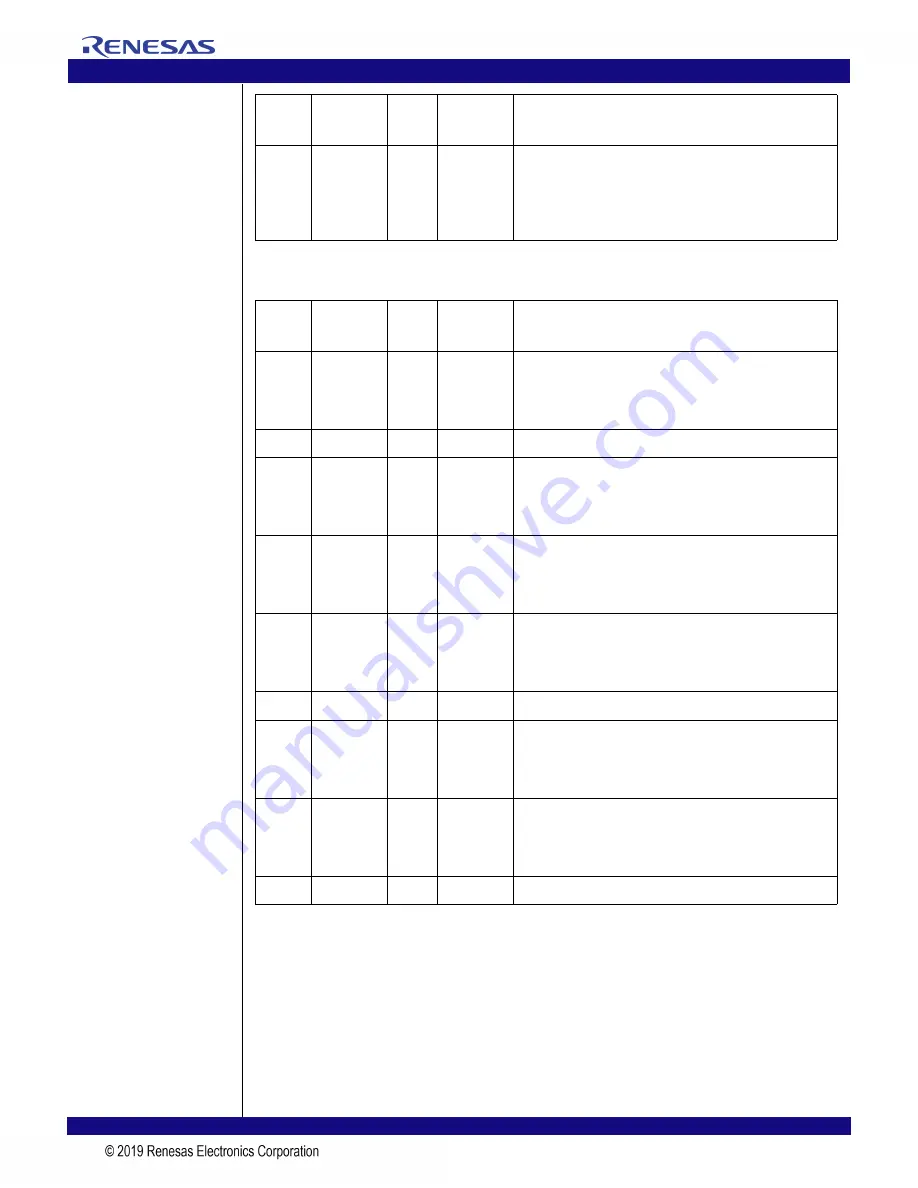

AERCEM - AER Correctable Error Mask (0x114)

31

SBE

RW1C

0x0

Sticky

Single Bit Error Status. When the Single Bit Error AER Reporting

Enable (SBEAEREN) bit is set in the Memory Error Control

(MECTL) register, this bit is set whenever a single bit error is

detected in any memory associated with the port.

When the SBEAEREN bit is cleared, this field is read-only zero.

Bit

Field

Field

Name

Type

Default

Value

Description

0

RCVERR

RW

0x0

Sticky

Receiver Error Mask. When this bit is set, the corresponding bit

in the AERCES register is masked. When a bit is masked in the

AERCES register, the corresponding event is not reported to the

root complex.

5:1

Reserved

RO

0x0

Reserved field.

6

BADTLP

RW

0x0

Sticky

Bad TLP Mask. When this bit is set, the corresponding bit in the

AERCES register is masked. When a bit is masked in the

AERCES register, the corresponding event is not reported to the

root complex.

7

BADDLLP

RW

0x0

Sticky

Bad DLLP Mask. When this bit is set, the corresponding bit in

the AERCES register is masked. When a bit is masked in the

AERCES register, the corresponding event is not reported to the

root complex.

8

RPLYROVR

RW

0x0

Sticky

Replay Number Rollover Mask. When this bit is set, the corre-

sponding bit in the AERCES register is masked. When a bit is

masked in the AERCES register, the corresponding event is not

reported to the root complex.

11:9

Reserved

RO

0x0

Reserved field.

12

RPLYTO

RW

0x0

Sticky

Replay Timer Time-Out Mask. When this bit is set, the corre-

sponding bit in the AERCES register is masked. When a bit is

masked in the AERCES register, the corresponding event is not

reported to the root complex.

13

ADVISO-

RYNF

RW

0x1

Sticky

Advisory Non-Fatal Error Mask.When this bit is set, the corre-

sponding bit in the AERCES register is masked. When a bit is

masked in the AERCES register, the corresponding event is not

reported to the root complex.

30:14

Reserved

RO

0x0

Reserved field.

Bit

Field

Field

Name

Type

Default

Value

Description

Summary of Contents for 89HPES24T3G2ZBAL

Page 8: ...IDT PES24T3G2 User Manual 6 February 22 2012 Notes...

Page 12: ...IDT Table of Contents PES24T3G2 User Manual iv February 22 2012 Notes...

Page 14: ...IDT List of Tables PES24T3G2 User Manual vi February 22 2012 Notes...

Page 16: ...IDT List of Figures PES24T3G2 User Manual viii February 22 2012 Notes...

Page 20: ...IDT Register List PES24T3G2 User Manual xii February 22 2012 Notes...

Page 32: ...IDT PES24T3G2 Device Overview PES24T3G2 User Manual 1 12 February 22 2012 Notes...

Page 72: ...IDT SMBus Interfaces PES24T3G2 User Manual 5 20 February 22 2012 Notes...

Page 76: ...IDT Power Management PES24T3G2 User Manual 6 4 February 22 2012 Notes...

Page 156: ...IDT Configuration Registers PES24T3G2 User Manual 8 74 February 22 2012 Notes...