Rabbit 3000A Instruction

Instruction Reference Manual

95

Description

•

LSDR

: While the data in BC does not equal 0, the memory location whose address is in DE is

loaded with the data at the address in HL. The data in BC, DE, and HL is then decremented.

This instruction then repeats until BC equals zero. If this instruction is prefixed by IOI or IOE,

the source will be in the specified I/O space.

•

LSIR

: While the data in BC does not equal 0, the memory location whose address is in DE is

loaded with the data at the address in HL. The data in BC is then decremented, and the data in

DE and HL is incremented. This instruction then repeats until BC equals zero. If this instruction

is prefixed by IOI or IOE, the source will be in the specified I/O space.

•

LSDDR

: While the data in BC does not equal 0, the memory location whose address is in DE is

loaded with the data at the address in HL. The data in BC and DE (but not HL) is then decre-

mented. This instruction then repeats until BC equals zero. If this instruction is prefixed by IOI

or IOE, the source will be in the specified I/O space.

•

LSIDR

: While the data in BC does not equal 0, the memory location whose address is in DE is

loaded with the data ta the address in HL. The data in BC is then decremented and DE incre-

mented (the data in HL remains unchanged). This instruction then repeats until BC equals zero.

If this instruction is prefixed by IOI or IOE, the source will be in the specified I/O space.

Add 1 clock for each iteration for the prefix if the prefix is IOI (internal I/O). If the prefix is IOE, add 2 clocks

plus the number of I/O wait states enabled. The V flag is cleared when BC transitions from 1 to 0. If the V

flag is not cleared another step is performed for the repeating versions of the instructions. Interrupts can occur

between different repeats, but not within an iteration. Return from the interrupt is to the first byte of the

instruction which is the I/O prefix byte if there is one. These instructions are implemented for the Rabbit

3000A.

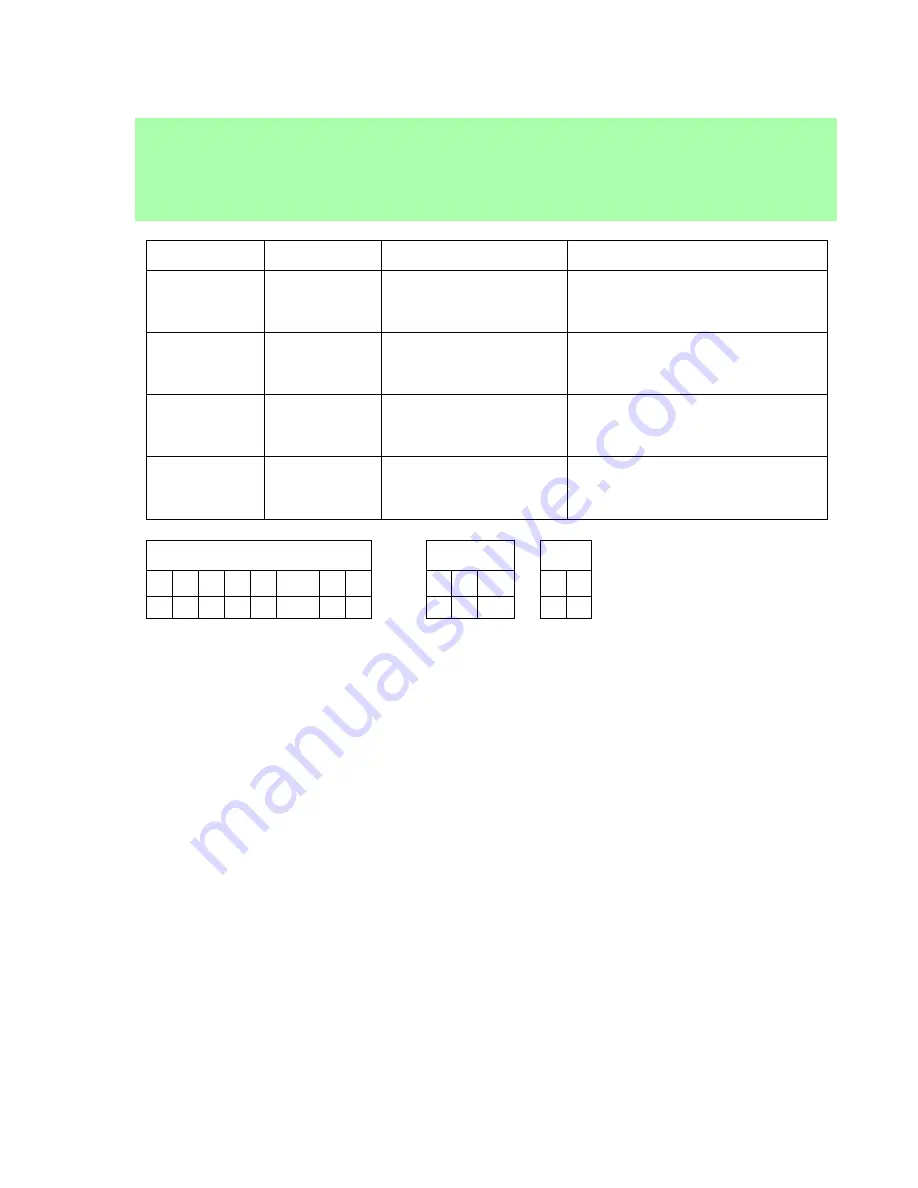

LSDR

LSIR

LSDDR

LSIDR

Opcode

Instruction

Clocks

Operation

ED F8

LSDR

6+7i

(2,2,1,(2,3,2)i,1)

(DE) = (HL); BC = BC-1;

DE = DE-1; HL = HL-1;

repeat while BC != 0

ED F0

LSIR

6+7i

(2,2,1,(2,3,2)i,1)

(DE) = (HL); BC = BC-1;

DE = DE+1; HL = HL+1;

repeat while BC != 0

ED D8

LSDDR

6+7i

(2,2,1,(2,3,2)i,1)

(DE) = (HL);

BC = BC-1; DE = DE-1;

repeat while BC != 0

ED D0

LSIDR

6+7i

(2,2,1,(2,3,2)i,1)

(DE) = (HL);

BC = BC-1; DE = DE+1;

repeat while BC != 0

Flags

ALTD

I/O

S

Z

L/V

C

F

R

SP

S

D

-

-

•

-

•

Summary of Contents for 2000

Page 2: ...ii Rabbit 2000 3000 Microprocessor...

Page 4: ...iv Rabbit 2000 Microprocessor...

Page 16: ...12 Rabbit 2000 3000 Microprocessor...

Page 164: ...160 Instruction Reference Manual...