5G Module Series

RM505Q-AE Hardware Design

RM505Q-AE_Hardware_Design 30 / 79

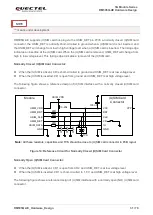

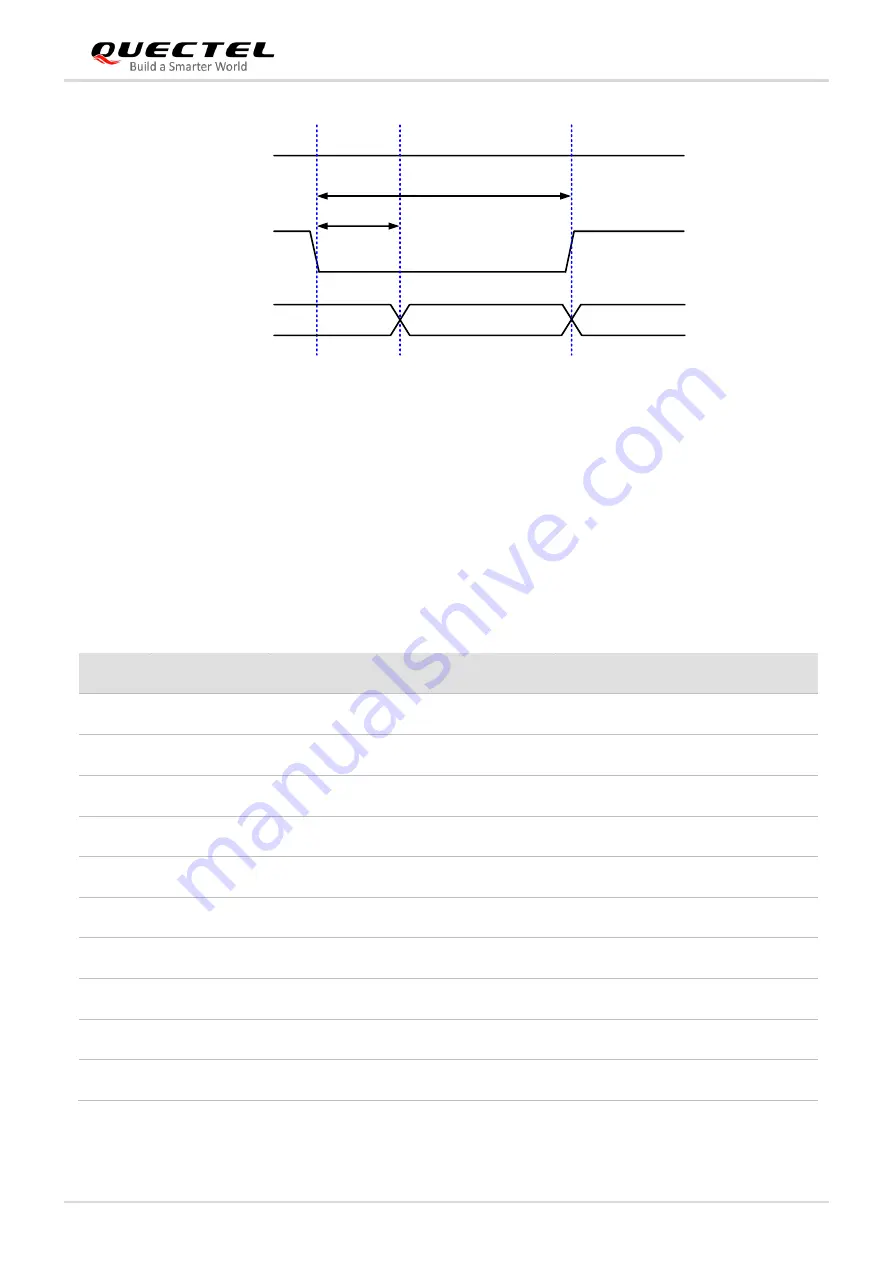

V

IL

≤ 0.5 V

VCC

≥ 200 ms

Resetting

Module Status

Running

RESET_N

Restart

≤ 700 ms

Figure 13: Resetting Timing of the Module

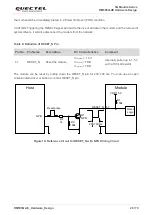

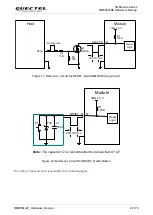

3.7. (U)SIM Interfaces

The (U)SIM interfaces circuitry meets ETSI and IMT-2000 requirements. Both Class B (3.0 V) and Class

C (1.8 V) (U)SIM cards are supported, and Dual SIM Single Standby* function is supported.

Table 9: Pin Definition of (U)SIM Interfaces

Pin No. Pin Name

I/O

Description

Comment

36

USIM1_VDD PO

Power supply for (U)SIM1 card

Class B (3.0 V) and Class C (1.8 V)

34

USIM1_DATA IO

(U)SIM1 card data

1.8/3.0 V power domain

32

USIM1_CLK

DO (U)SIM1 card clock

1.8/3.0 V power domain

30

USIM1_RST

DO (U)SIM1 card reset

1.8/3.0 V power domain

66

USIM1_DET

DI

(U)SIM1 card insertion detection. Internally pulled up to 1.8 V

48

USIM2_VDD PO

Power supply for (U)SIM2 card

Class B (3.0 V) and Class C (1.8 V)

42

USIM2_DATA IO

(U)SIM2 card data

1.8/3.0 V power domain

44

USIM2_CLK

DO (U)SIM2 card clock

1.8/3.0 V power domain

46

USIM2_RST

DO (U)SIM2 card reset

1.8/3.0 V power domain

40

USIM2_DET

DI

(U)SIM2 card insertion detection. Internally pulled up to 1.8 V