PHYTEC

Page 19

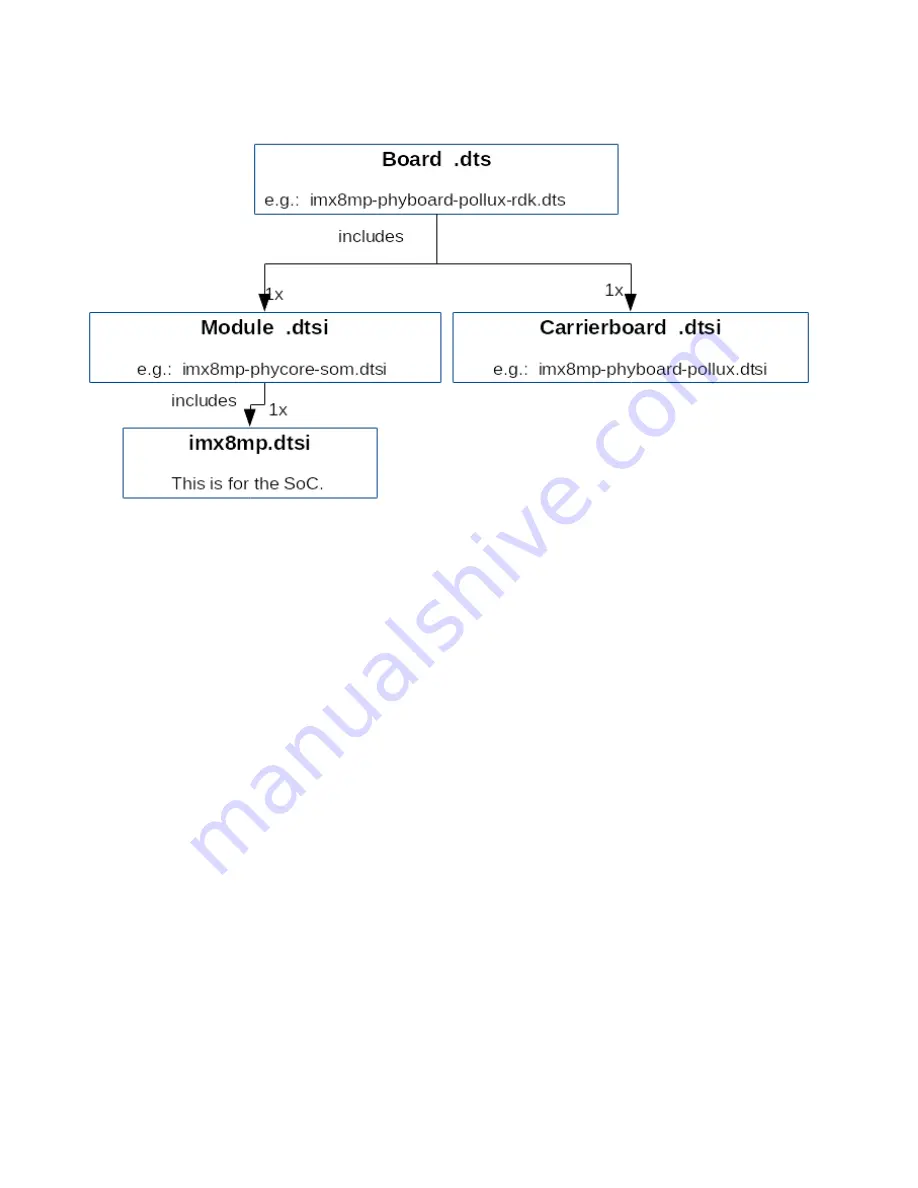

The module includes file

which contains all devices which are mounted on the module, such as PMIC and RAM. Devices that come from the i.

Modul .dtsi

MX 8M Plus SoC but are just routed down to the carrier board are not part of the

. These devices are included in the

. The

Module .dtsi

Carrierboard .dtsi

Bo

includes the carrier board and module nodes. It also adds partition tables and enables all hardware configurable nodes of the carrier board or the

ard .dts

module (i.e. the

shows the special characteristics of the board configuration). For example, there are phyCORE-i.MX 8M Plus SOMs which may

Board .dts

or may not have a SPI NOR flash mounted. The converter is enabled (if available) in the

and not in the

.

Board .dts

Module .dtsi

Accessing Peripherals

/produkte/software/yocto/phytec-unified-yocto-bsp-releases/

and click the corresponding BSP release. here you can find all hardware supported in the

For information about all our supported i.MX8 variants, visit our web page at

.

http://www.phytec.de/produkte/nxp/imx-8/

To achieve maximum software re-use, the

kernel offers a sophisticated infrastructure that layers software components into board-specific parts. The

Linux

BSP tries to modularize the kit features as far as possible. This means that when a customized baseboard or even a customer-specific module is

developed, most of the software support can be re-used without error-prone copy-and-paste. The kernel code corresponding to the boards can be found in

device trees (DT) under

.

linux/arch/arm64/boot/dts/freescale/*.dts*

In fact, software re-use is one of the most important features of the Linux kernel, especially of the ARM implementation which always has to fight with an

insane number of possibilities of the System-on-Chip CPUs. The whole board-specific hardware is described in DTs and is not part of the kernel image

itself. The hardware description is in its own separate binary, called the Device Tree Blob (DTB) (section

).

Please read section

to get an understanding of our i.MX8 BSP device tree model.

PHYTEC i.MX 8M Plus BSP Device Tree Concept

The following sections provide an overview of the supported hardware components and their operating system drivers on the i.MX8 platform. Further

changes can be ported upon customer request.

i.MX 8M Plus Pin Muxing

The i.MX 8M Plus SoC contains many peripheral interfaces. In order to reduce package size and lower overall system cost while maintaining maximum

functionality, many of the i.MX 8M Plus terminals can multiplex up to eight signal functions. Although there are many combinations of pin multiplexing that

are possible, only a certain number of sets called IO sets, are valid due to timing limitations. These valid IO sets were carefully chosen to provide many

possible application scenarios for the user.

Please refer to the

for more information about the specific pins and muxing capabilities.

NXP i.MX 8M Plus Reference Manual

The IO set configuration, also called muxing, is done in the Device Tree. The driver

reads the DT's node

, and does the appropriate

pinctrl-single

fsl,pins

pin muxing.