Appendix B: Flash BIOS

F000h segment with 0FFh. Initializes the Microsoft IRQ Routing Table. Prepares the

runtime language module. Disables the system configuration display if needed.

A4

Initialize runtime language module.

A7

Displays the system configuration screen if enabled. Initialize the CPU’s before boot, which

includes the programming of the MTRR’s.

A8

Prepare CPU for OS boot including final MTRR values.

A9

Wait for user input at config display if needed.

AA

Uninstall POST INT1Ch vector and INT09h vector. Deinitializes the ADM module.

AB

Prepare BBS for Int 19 boot.

AC

End of POST initialization of chipset registers.

B1

Save system context for ACPI.

00

Passes control to OS Loader (typically INT19h).

61-70

OEM POST Error.

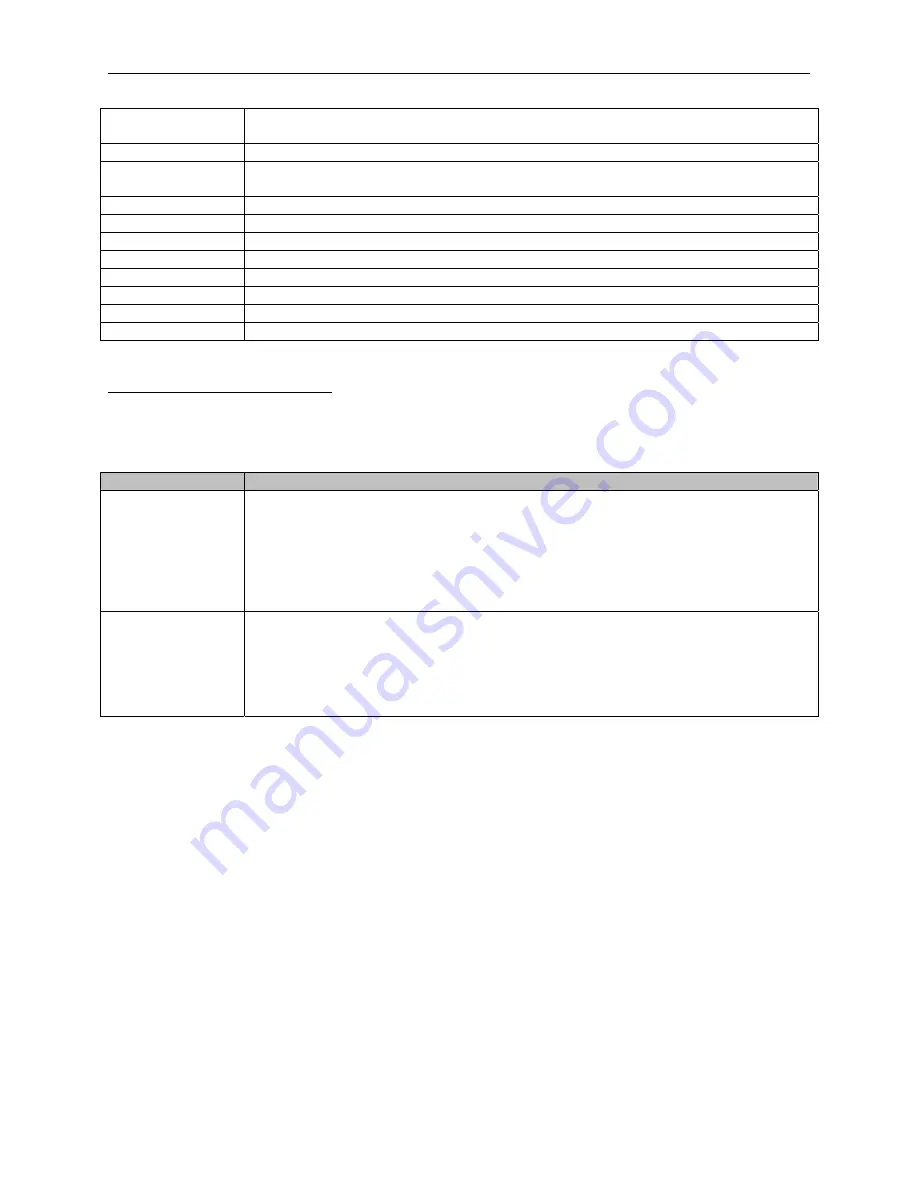

Table B-4 DIM Code Checkpoints

The Device Initialization Manager (DIM) gets control at various times during BIOS POST to initialize different

system busses. The following table describes the main checkpoints where the DIM module is accessed:

Checkpoint Code

Description

2A

Initialize different buses and perform the following functions: Reset, Detect, and Disable

(function 0); Static Device Initialization (function 1); Boot Output Device Initialization

(function 2). Function 0 disables all device nodes, PCI devices, and PnP ISA cards. It also

assigns PCI bus numbers. Function 1 initializes all static devices that include manual

configured onboard peripherals, memory and I/O decode windows in PCI-PCI bridges, and

noncompliant PCI devices. Static resources are also reserved. Function 2 searches for and

initializes any PnP, PCI, or AGP video devices.

38

Initialize different buses and perform the following functions: Boot Input Device

Initialization (function 3); IPL Device Initialization (function 4); General Device

Initialization (function 5). Function 3 searches for and configures PCI input devices and

detects if system has standard keyboard controller. Function 4 searches for and configures

all PnP and PCI boot devices. Function 5 configures all onboard peripherals that are set to

an automatic configuration and configures all remaining PnP and PCI devices.

While control is in the different functions, additional checkpoints are output to port 80h as a word value to identify

the routines under execution. The low byte value indicates the main POST Code Checkpoint. The high byte is

divided into two nibbles and contains two fields. The details of the high byte of these checkpoints are as follows:

HIGH BYTE XY

The upper nibble 'X' indicates the function number that is being executed. 'X' can be from 0 to 7.

0 = func#0, disable all devices on the BUS concerned.

1 = func#1, static devices initialization on the BUS concerned.

2 = func#2, output device initialization on the BUS concerned.

3 = func#3, input device initialization on the BUS concerned.

4 = func#4, IPL device initialization on the BUS concerned.

5 = func#5, general device initialization on the BUS concerned.

6 = func#6, error reporting for the BUS concerned.

7 = func#7, add-on ROM initialization for all BUSes.

8 = func#8, BBS ROM initialization for all BUSes.

The lower nibble 'Y' indicates the BUS on which the different routines are being executed. 'Y' can be from 0 to 5.

0 = Generic DIM (Device Initialization Manager).

51

StockCheck.com

Downloaded from StockCheck.com

Summary of Contents for MicroATX Express

Page 1: ... Phoenix MicroATX Express Motherboard Installation Guide ...

Page 2: ...StockC heck com Downloaded from StockCheck com ...

Page 26: ...Phoenix MicroATX Express Installation Guide 18 StockC heck com Downloaded from StockCheck com ...

Page 61: ...Appendix B Flash BIOS User s Notes 53 StockC heck com Downloaded from StockCheck com ...

Page 67: ...Appendix C Industrial Devices 59 StockC heck com Downloaded from StockCheck com ...

Page 71: ...StockC heck com Downloaded from StockCheck com ...

Page 72: ...MN P45MX 01 StockC heck com Downloaded from StockCheck com ...