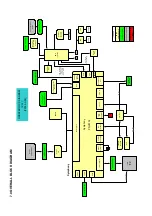

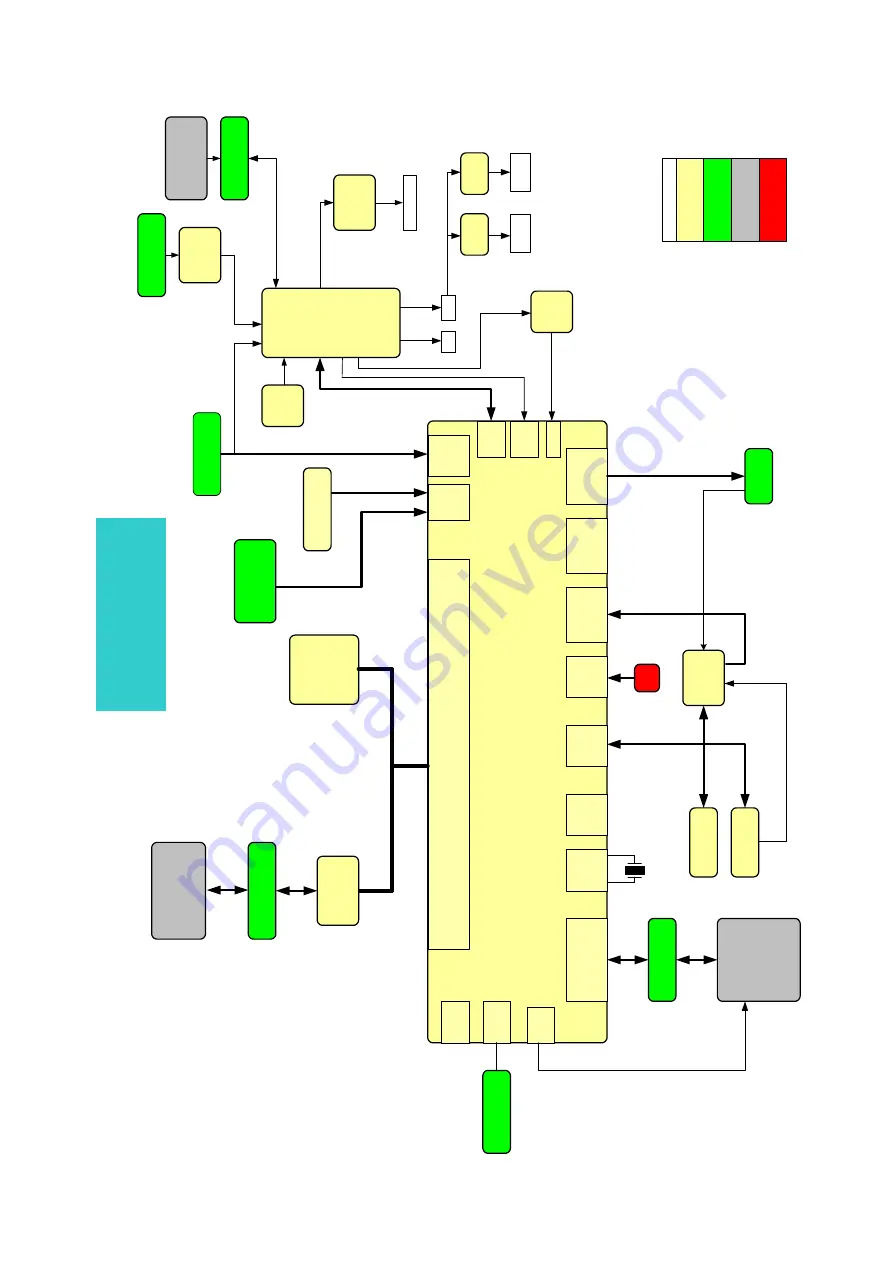

7.0 OVERALL BLOCK DIAGRAM

Symp

ho

ny

PN

X0

10

2

H

DD C

onnector

Cor

nice

3G

B

Ha

rd

Di

sk

A

nalog keys

on the 5-key R

emote

SD

RA

M

Memory Bus

GP

A

PMU

LTC3455

A

C

/DC

Input Jack

Rever

se +

O

vervoltage

pr

otecti

on

US

B Mi

ni

-B

So

ck

et

US

B

2.0

Hi

gh

S

peed

GP

IO

GP

A

LDO

B

att

ery C

onnector

1 Cell

Li-polymer

B

atter

y

Po

w

er O

n

logic

1V

8

3V

1

3V

0_A

LC

D Connector

LCD

Inter

face

LCM

96x64

B/

W

LNA

MIC

amplifier

Li

ne

In

12MH

z

syscloc

k

Li

ne Out

Headphone

Out

32K

Hz

RT

Ccloc

k

I2C

inte

rface

EE

PR

O

M

M

24C

08

RT

C

FM tuner

Headphone

connector

UA

RT

C

onstant

Current

S

ource

V

B

acklight

JT

AG

Multi

ICE

connector

+

m

ode s

election

swi

tches

Reset

logic

Re

se

t

A

nalog K

eys on the

D

evice

U

SB_

SU

SPE

N

D

U

SB_

H

IG

H

_PW

R

PWR

_

AC

K

CHG

_S

T

A

T

U

S

BAT

T

_L

O

W_

N

LE

GE

ND

BO

A

R

D

COM

P

ONE

N

T

S

CON

N

E

C

T

O

RS

EX

T

E

R

N

A

L DE

VI

CE

S

H

DD084 Onl

y, not for

PSA

61

0

MIC

Sym

phony

Cor

nice

TIC

GP

IO

LCD_

B

L_

C

T

R

L

B

A

T

_

LEVE

L

CHG

_

CURRE

NT

FM

_

A

NT

RT

C_

O

U

T

LD

O

3V

0_RF

HDD08

4 BLO

C

K DIAGRA

M

(V1

.2)

(20

05

-0

5-

09

)

Summary of Contents for HDD082

Page 22: ...9 0 COMPONENT LAYOUT ...

Page 23: ...9 0 COMPONENT LAYOUT ...

Page 24: ...9 0 COMPONENT LAYOUT ...